Xilinx虚拟输入/输出(VIO)IP核详细介绍及使用示例

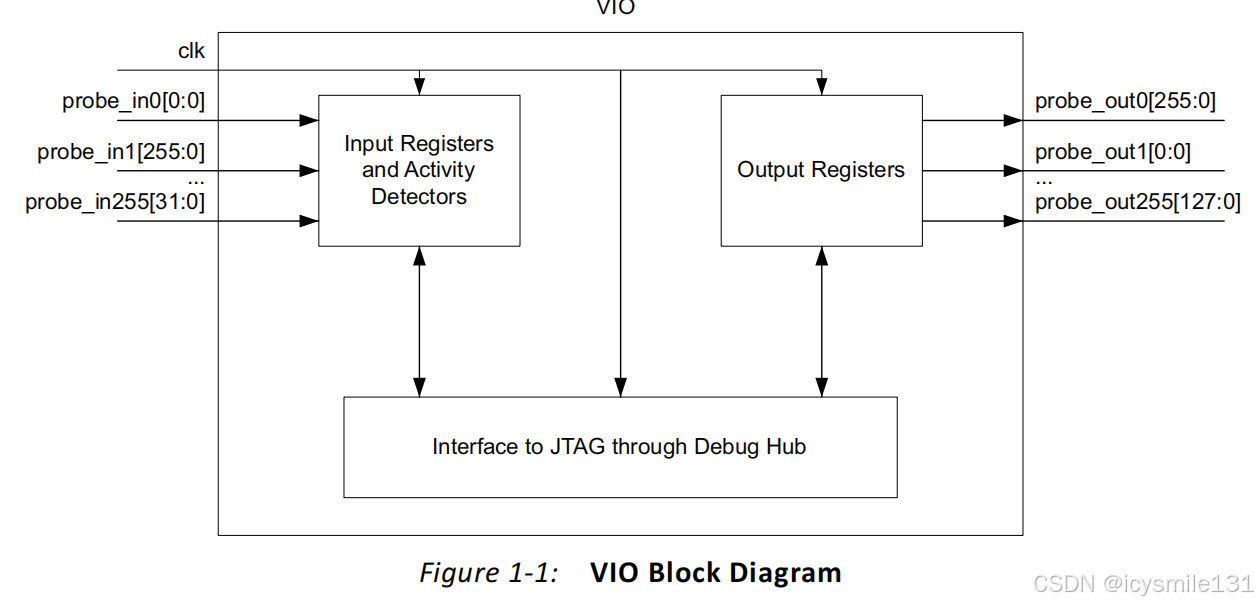

LogiCORE™ IP虚拟输入/输出(VIO)内核是一款可定制化的内核,能够实时监控和驱动FPGA(现场可编程门阵列)内部信号。其输入和输出端口的数量及位宽均可根据需求定制,以便与FPGA设计进行接口对接。由于VIO内核与被监控和/或驱动的设计保持同步,因此应用于您设计中的所有设计时钟约束,同样也会应用于VIO内核内部的组件。与该内核进行运行时交互需要使用Vivado®逻辑分析仪功能。

VIO(虚拟输入/输出)内核中提供两种类型的信号:

• 输入探针(Input Probes)

• 输出探针(Output Probes)

(1)输入探针(Input Probes)

这些输入信号通过连接到CLK输入端口的设计时钟进行寄存。输入值会定期被读取,并在Vivado®逻辑分析仪功能中显示。

其作用是 实时监控 FPGA 内部信号的状态,因此它应该连接到 FPGA 设计中的输出信号(即内部逻辑产生的信号),而不是 FPGA 的物理输入引脚(如外部 GPIO、按键等)。

-

功能:VIO 的

probe_in是一个 只读监控接口,用于在调试阶段通过 Vivado Hardware Manager 实时观察