复旦大学发布全球首款二维半导体芯片——无极

近日,二维半导体芯片取得里程碑式突破。2025年4月2日,复旦大学集成芯片与系统全国重点实验室周鹏、包文中联合团队以《基于二维半导体的RISC-V 32比特微处理器》(“A RISC-V 32-Bit Microprocessor Based on Two-dimensional Semiconductors”)[1]为题在《Nature》期刊发表重大成果,宣布成功研制全球首款基于二维半导体材料的32位RISC-V架构微处理器“无极(WUJI)”。

一、研究背景

随着漏致势垒降低、界面散射导致的迁移率下降以及有限的电流开关比等问题的出现,传统硅基半导体逐渐逼近其物理极限,寻找“后硅时代”的新型半导体材料成为了研究热点。原子级厚度的二维(2D)半导体材料,如二硫化钼(MoS2),因其独特的物理特性而备受关注,被视为极具潜力的解决方案,作为一种新兴电路架构,二维半导体有望满足当前对边缘计算和智能传感器等领域的要求[1]。

研究者对二维半导体材料的研究已持续十余年。最初的研究集中在基础材料的制备(如机械剥离法获得小尺寸样品)和物性探索。近年来,研究重心转向了更大规模、更高质量的材料生长和器件制造。重要的进展包括实现了晶圆级(例如12英寸)二维材料(如MoS2)的均匀生长、能带结构调控、低电阻源漏接触(例如利用半金属接触)以及高质量介质层(如高k介质)的集成等。这些单点技术的突破使得单个二维晶体管的性能指标已经可以与国际器件与系统路线图(IRDS)中的预期相媲美。

尽管取得了显著进展,但将二维半导体从单个器件推向大规模集成电仍面临巨大挑战:

1.材料制备与工艺协同优化:二维材料仅有原子级厚度,其载流子对周围环境极其敏感。这要求开发出针对性的、创新的加工技术,同时还要确保这些技术能与主流的硅基CMOS工艺兼容,以实现可行的制造。

2.从晶体管到电路的跨越:要将均匀分布、性能一致的二维晶体管集成为功能电路,需要借鉴硅基集成电路制造中前端和后端的经验,并进行大量的材料与工艺协同优化研究。虽然单个或小阵列二维晶体管的制备良率可以很高,但要实现超大规模集成电路,对材料均匀性、工艺稳定性和缺陷控制提出了极高的要求。在本文之前,笔者搜索到国际上集成度最高的二维半导体数字电路仅含有115个晶体管[2]。

3.创新电路架构:传统硅基电路积累下来的电路架构方面的经验可能不适合二维晶体管发挥最佳性能。目前主流研究多基于单一极性的二位晶体管,使得其在使用方式上相较于COMS存在区别,需要探索新的电路设计。

复旦大学周鹏、包文中教授团队长期致力于二维半导体材料与器件的研究。该团队在二维材料晶圆级生长、器件工艺(如顶栅结构开发、接触工程、介质集成)等方面积累了深厚基础。他们认识到工艺优化对于提升器件和电路性能的重要性,并引入机器学习等方法来系统性地分析和优化复杂的制造流程[3],实现了晶圆级二维半导体功能电路。

二、具体工作

这次发布的“无极”芯片是周鹏、包文中教授团队多年研究的集大成者。他们在4英寸二硫化钼(MoS2)晶圆上,利用与主流硅基CMOS工艺兼容的顶栅晶体管结构和四层金属互连技术,成功集成了超过5900个MoS2晶体管,构建了一个能够执行标准RISC-V 32位整数指令集(RV32I)的微处理器原型RV32-WUJI,在器件工艺协同优化、从晶体管到电路、新的电路架构三方面取得重要突破。配套的核心基础单元库包括25种完整二维半导体逻辑单元,制造良率达到99.77%。

1.器件工艺协同优化:

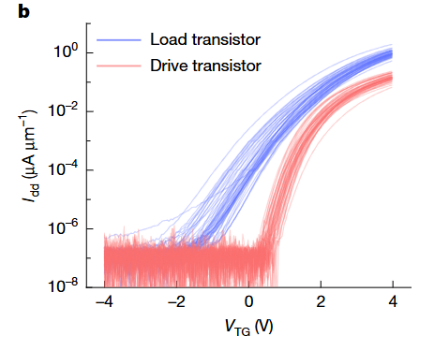

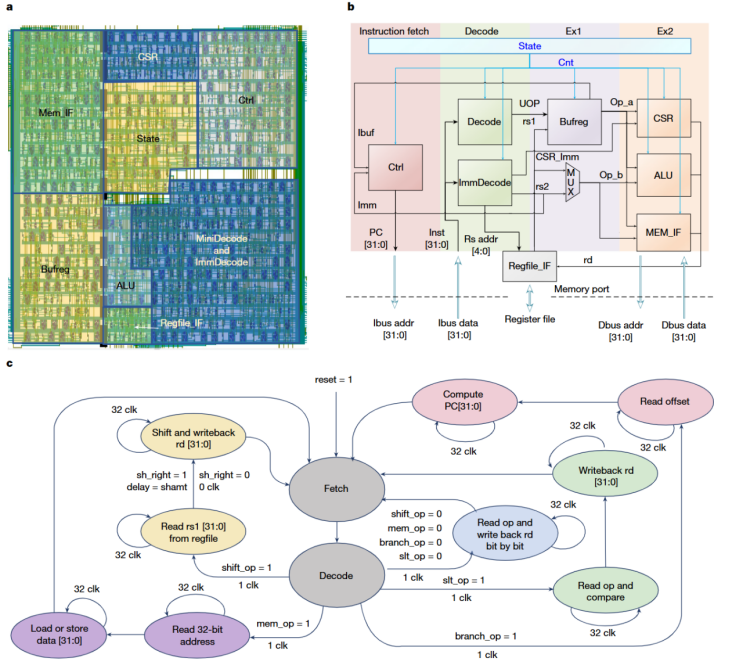

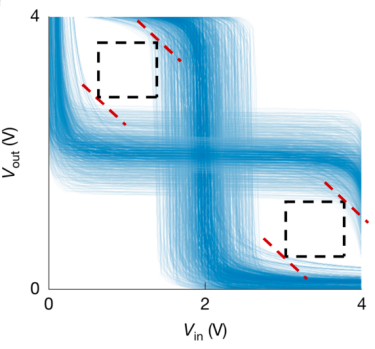

原子层厚度的沟道对任何工艺处理都极为敏感,传统硅基集成电路工艺难以直接应用。先前的研究已证实,对FET阵列进行晶圆级处理能够实现高良率。然而,将多个功能单元集成到单个芯片中形成超大规模集成电路要复杂得多。为解决这一问题,“无极”芯片采用顶部栅极晶体管结构,这种结构有助于与现有CMOS技术集成。在阈值电压(VTH)控制方面,传统的离子注入法会破坏二维晶体结构,因此,团队通过两种方法来调节VTH:(1)应用具有不同功函数的铝(Al)或金(Au)金属栅极,使MoS2沟道处于积累态或耗尽态(见图1);(2)通过优化种子层,在二硫化钼沟道上沉积高k介电层。这些组合策略可以有效地调节二硫化钼场效应晶体管(MoS2 FET)的VTH,以实现逻辑连接层(M1)和栅极层在电路层面的匹配和优化。此外,针对二维半导体工艺复杂、对器件性能影响因素多的问题,团队运用机器学习方法,通过“原子级界面精准调控”与“全流程AI算法优化”的双引擎,实现工艺参数的自动化优化。团队通过分析各工艺步骤对器件性能的贡献,优化工艺流,使晶体管总体良品率达到 99.92%,保障了二维超大规模集成电路制造的可行性。

图1 构成反相器的负载晶体管和驱动晶体管的转移特性曲线

2.从晶体管到电路:

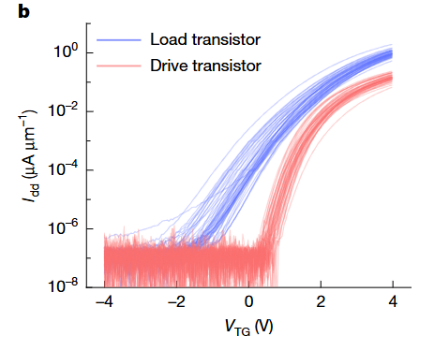

图2展示了RV32-WUJI的整体结构,包括其在4英寸蓝宝石晶圆上的布局(图2a)、芯片的物理层结构(图2b)、典型逻辑门单元的SEM图像(图2c)以及晶体管沟道区域的扫描电子显微镜图(图2d)。在前端制程(FEOL),直接在合成的MoS₂薄膜上制造顶部栅控晶体管,源极和漏极层(M0)以及栅极层在这一过程中形成。从图2c的SEM图像可以看到OAI21、AOI22等逻辑门单元的微观结构,这是前端制程的成果体现。后端制程(BEOL)则形成M1和模块连接层(M2和M3),将晶体管连接成基本逻辑单元,再组合成完整功能芯片。图2c展示了这些连接层在构建逻辑单元中的作用。在这个过程中,对材料和工艺进行了系统的协同优化,精心优化层间介质沉积,确保后端工艺中反相器的参考开关阈值电压(VM)偏移量在可接受范围内,从而实现了从晶体管到功能电路的可靠构建。基于优化的逆变器特性,构建了包含25种逻辑单元的标准单元库。通过测试和计算逻辑单元的输入输出负载噪声容限,测试结果说明n型MoS₂晶体管逻辑电路设计中的负载匹配问题已被解决,为实现复杂的数字逻辑电路提供了基础。

图2 RV32-WUJI芯片图

3.创新电路架构:

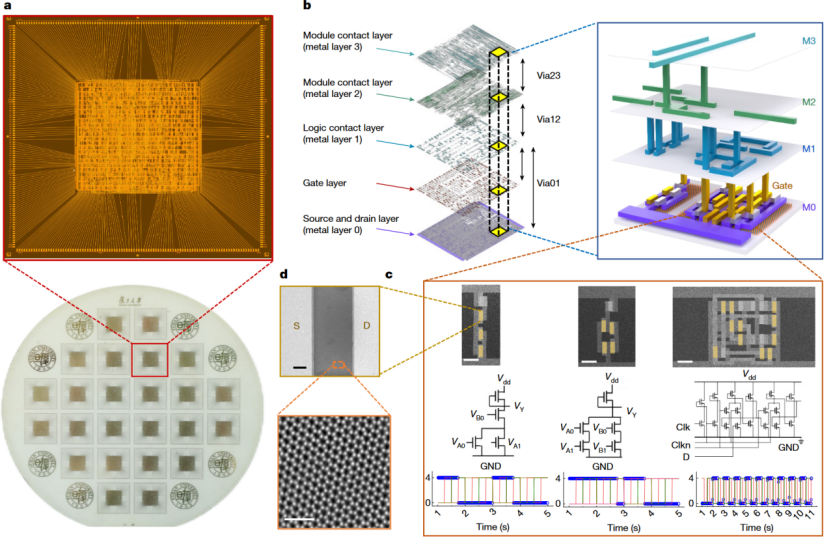

RV32-WUJI芯片基于RV32I指令集,图3展示了其架构和设计。从图3a可以看到芯片包含1位算术逻辑单元、控制状态寄存器模块、指令解码模块等多个模块。图3b展示了数据在这些模块中的处理路径,在指令执行过程中,控制模块将指令发送到指令总线,数据经过算术逻辑单元处理,不同操作数来源不同,最终完成运算。这种串行处理架构降低了静态功耗和硬件开销,适合边缘嵌入式环境的小型物联网设备。从图3c的状态机示意图可以看出指令的执行流程,不同类型的指令(如加法、移位、分支等)按照特定的步骤在多个时钟周期内完成运算和数据处理。通过实际测试,RV32-WUJI芯片可以实现加法运算的执行波形,验证了其在新架构下的功能正确性,笔者将在后文中详细介绍相关测试。此外,RV32-WUJI芯片在1kHz频率下运行时功耗仅为0.43mW,体现了这种新架构在低功耗应用场景中的优势。

图3 RV32-WUJI的设计与整体结构图

三、性能与应用

在复旦大学取得突破之前,国际上最高的二维半导体数字电路集成度仅仅为115个晶体管,由奥地利维也纳工业大学团队在2017年实现[2]。集成度提升的核心难题在于:原子级的精密元件组成完整的集成电路系统,受制于工艺精度与规模匀性的协同良率控制。“无极”经过五年攻关,成功将芯片从阵列级或器件级推向系统级集成,集成了5900个晶体管,可以串行实现37种32位RISC-V指令,达到国际最优水平。团队在芯片中制造了900个反相器阵列,每个阵列包含30×30个反相器,“反相器是一个非常基础且重要的逻辑电路,它的良率直接反映了整个芯片的质量。”复旦大学微电子学院教授周鹏介绍,二维材料不像硅晶圆可以通过直拉法生长出高质量的大尺寸单晶,而是需要通过化学气相沉积(CVD)法来生长,这就导致了材料本身的缺陷和不均匀性。如图4所示,900个反相器中的898个反相器逻辑功能完好无损,良率达到99.77%。

图4 “无极”中反相器良率达到99.77%

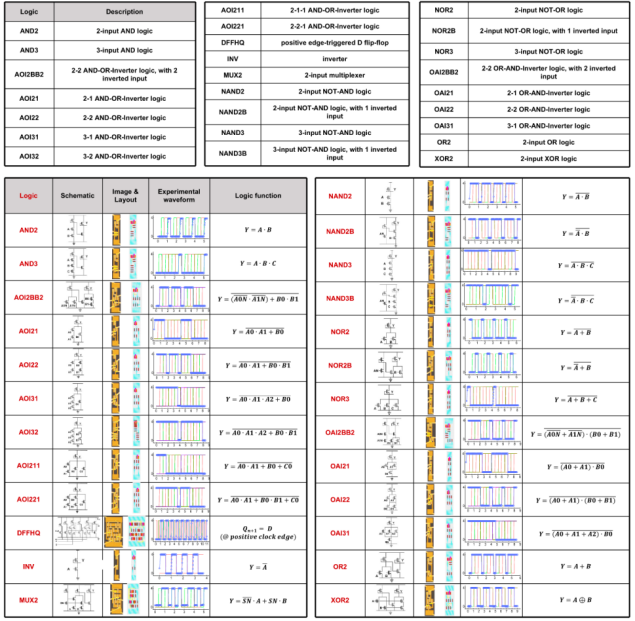

“无极” 支持 32 位 RISC-V 整型指令集(RV32I),在 1kHz 时钟频率下可串行执行37种指令,实现最大42亿次数据加减运算,支持GB级数据存储与10亿条指令程序编写。如图5所示,“无极”设计了包含25种逻辑模块的MoS2标准单元库(standard cell library),并对他们进行了测试与总结,图5中展示了这25种模块的原理图、显微图像、波形与逻辑函数。

图5 MoS2标准单元库与各模块原理图、显微图、波形与逻辑函数

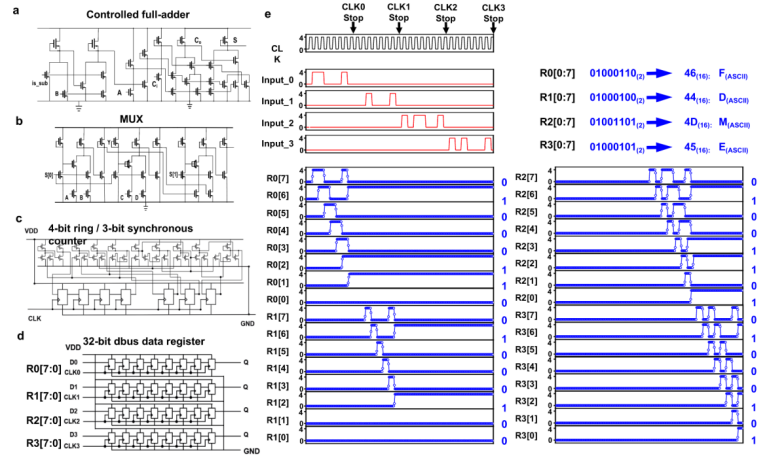

研究团队还对“无极”的四个核心模块进行了测试,分别为全加器、4输入选择器、4位环形计数器和32位寄存器。图6中展示了四种模块的原理图及验证功能的测量波形。

图6 四种核心模块原理图及功能测试

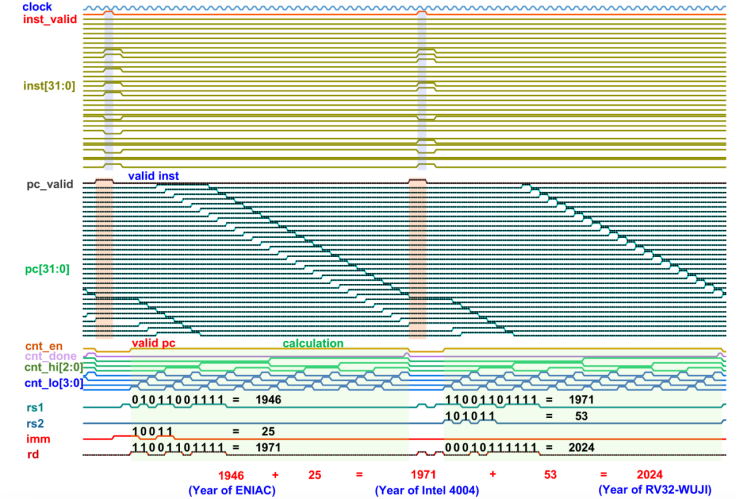

图7展示了无极进行逻辑计算时各信号的波形图,演示了ENIAC、Intel 404与无极在诞生年份上的加法运算联系。

图7 将 ENIAC 和 Intel 4004 以及无极诞生年实现了加法上的运算联系

“我们的最终目标是将技术送到千家万户,建立开放兼容的用户生态。”复旦微电子学院研究员韩军在本次工作中负责RISC-V架构设计。他介绍,选择这一架构意味着对接全球技术标准且无需依赖封闭架构,未来可自主构建用户生态,不受制于国外厂商的架构和IP专利。同时,在团队开发的二维半导体集成工艺中,70%左右的工序可直接沿用现有硅基产线成熟技术,而核心的二维特色工艺也已构建包含20余项工艺发明专利,结合专用工艺设备的自主技术体系,为产业化落地铺平道路。

在未来,团队计划进一步提升芯片集成度至万级晶体管,并开发专用工艺平台。本文通讯作者周鹏教授表示:“二维半导体不会取代硅基芯片,而是形成互补生态。我们正与企业合作,推动核心工艺的产业化应用。”下一步,复旦大学研究团队将聚焦边缘计算、AI 推理等场景,探索感存算一体化集成,为下一代智能设备提供低功耗解决方案,为全球半导体技术革新注入中国力量。

参考文献

[1] Ao, M., Zhou, X., Kong, X., Gou, S., Chen, S., Dong, X., ... & Zhou, P.. A RISC-V 32-bit microprocessor based on two-dimensional semiconductors. Nature, 1-8 (2025).

[2] Wachter, S., Polyushkin, D., Bethge, O. et al. A microprocessor based on a two-dimenional semiconductor. Nature Communications, 8, 14948 (2017).

[3] Chen, X., Xie, Y., Sheng, Y. et al. Wafer-scale functional circuits based on two dimensional semiconductors with fabrication optimized by machine learning. Nature Communications, 12, 5953 (2021).