可配置多功能门芯片的12种用法推导——基于74LVC1G97芯片(附1G98、1G57、1G58、1G99用法)

可配置多功能门,英文Configurable Multiple Function Gate,是一种特殊且有趣的逻辑门芯片。市面上常见且易购得的型号有5大类,分别为1G57、1G58、1G97、1G98、1G99。

1G57、1G58、1G97、1G98均为6-pin芯片,1G57和1G58的输出互为反相,1G97和1G98的输出互为反相,它们均能够实现一些2输入基本逻辑门,但均有局限,互为补充。

1G99为8-pin芯片,是全功能逻辑门,能够实现任意一种2输入基本逻辑门,同时额外支持了三态输出,可替代上述任意一款芯片。

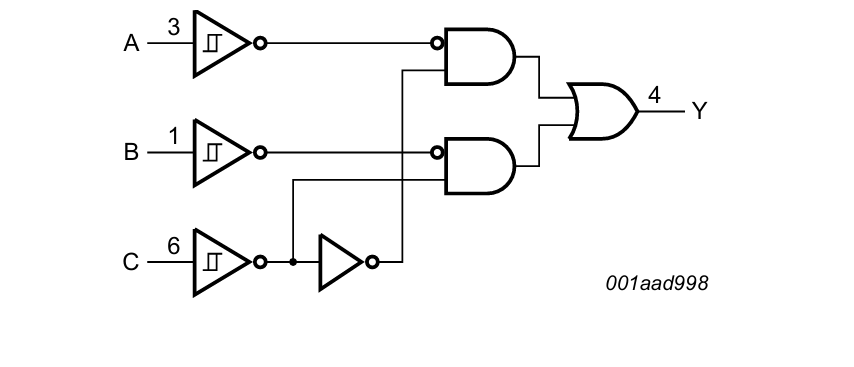

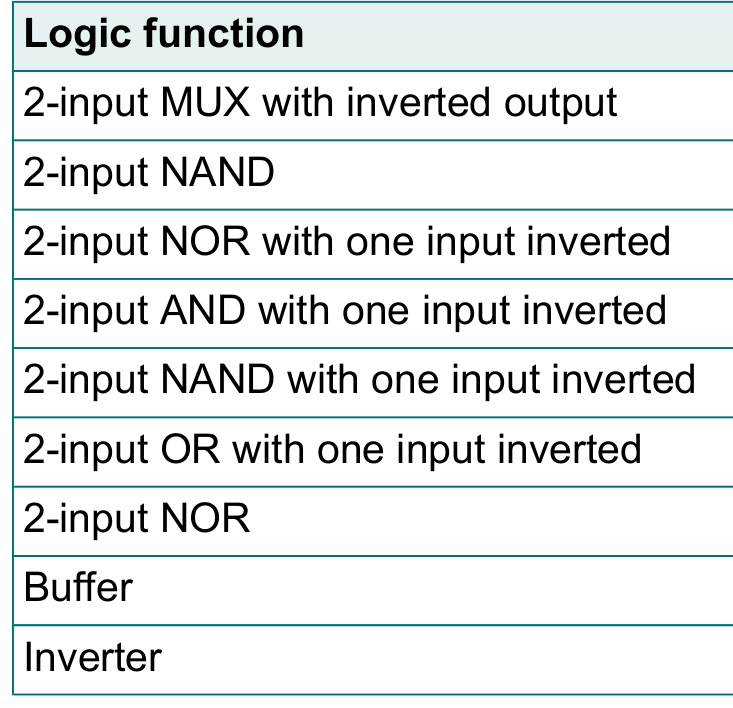

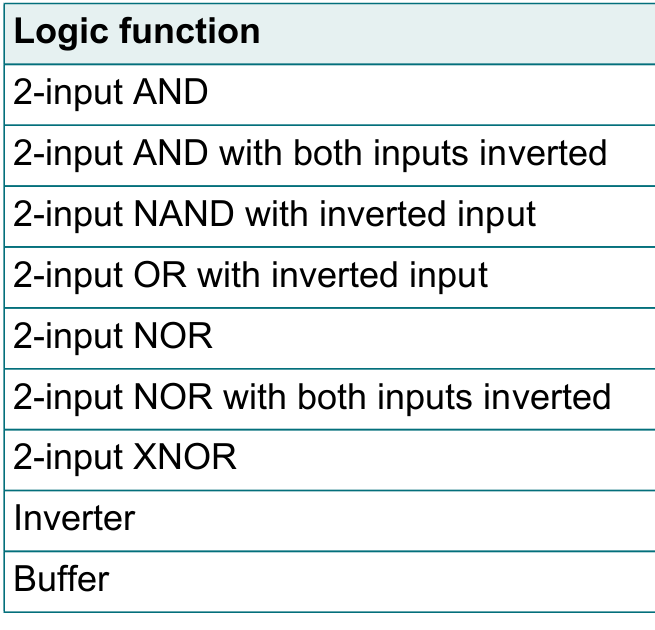

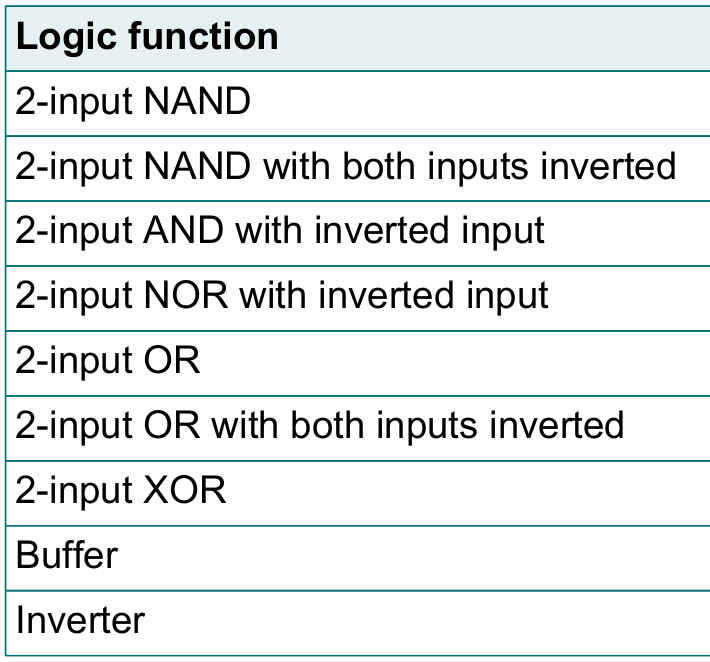

74LVC1G97是一款6引脚的简单逻辑芯片,有3个输入引脚和1个输出引脚,另有1个电源引脚和1个接地引脚。逻辑示意图如下

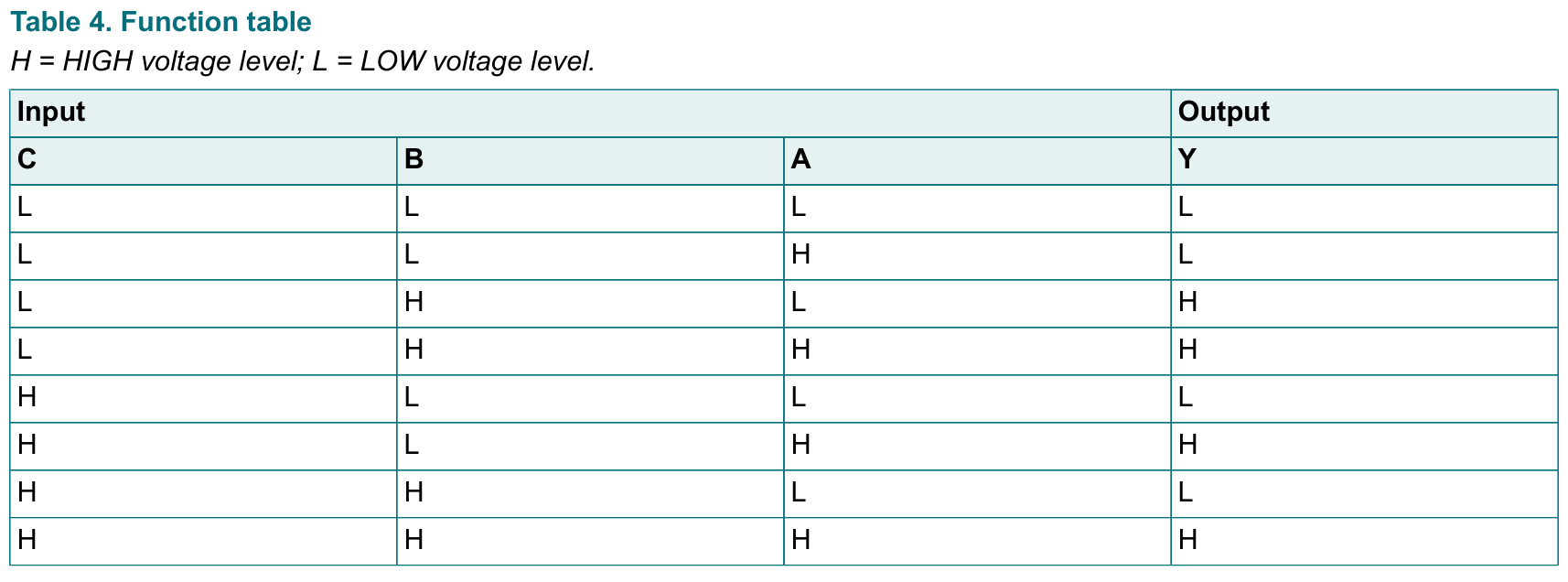

数据手册中给出了3个输入和1个输出的8行真值表。

抄录为电子表格

| C | B | A | Y |

|---|---|---|---|

| L | L | L | L |

| L | L | H | L |

| L | H | L | H |

| L | H | H | H |

| H | L | L | L |

| H | L | H | H |

| H | H | L | L |

| H | H | H | H |

2个输入引脚引出,1个输入引脚固定拉高或拉低时,该芯片可作为2输入逻辑门使用,有如下8种用法:

C作为设置信号

C拉低,此接法下,Y=B,A不影响输出

| C | B | A | Y |

|---|---|---|---|

| L | L | L | L |

| L | L | H | L |

| L | H | L | H |

| L | H | H | H |

C拉高,此接法下,Y=A,B不影响输出

| C | B | A | Y |

|---|---|---|---|

| H | L | L | L |

| H | L | H | H |

| H | H | L | L |

| H | H | H | H |

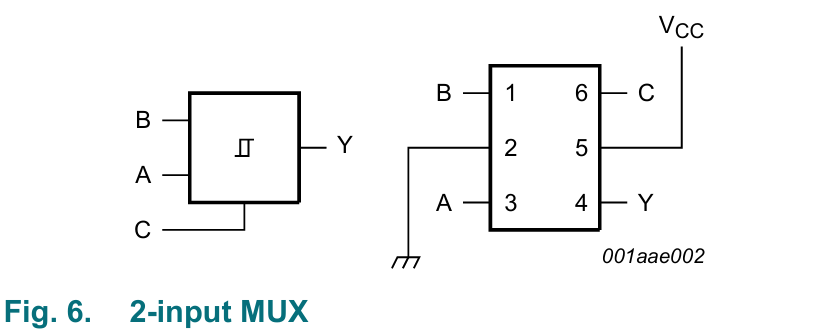

这两种接法共同组成了2:1 Mux,C用于设定选通,C=1时,Y=A;C=0时,Y=B

B作为设置信号

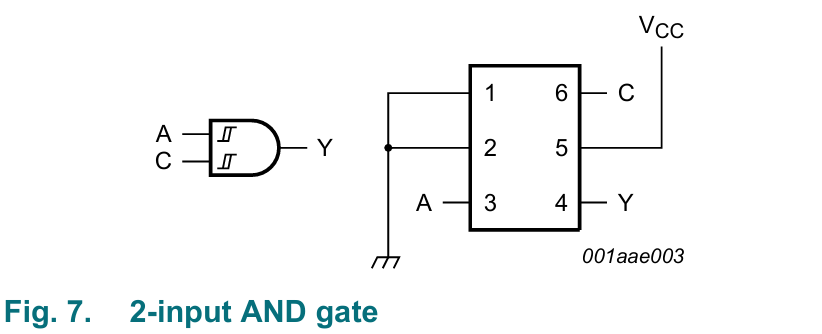

B拉低,此接法下,仅当A=C=1时,Y=1,因此不难发现Y=A&C,属于“与门”(AND Gate)用法

| B | C | A | Y |

|---|---|---|---|

| L | L | L | L |

| L | L | H | L |

| L | H | L | L |

| L | H | H | H |

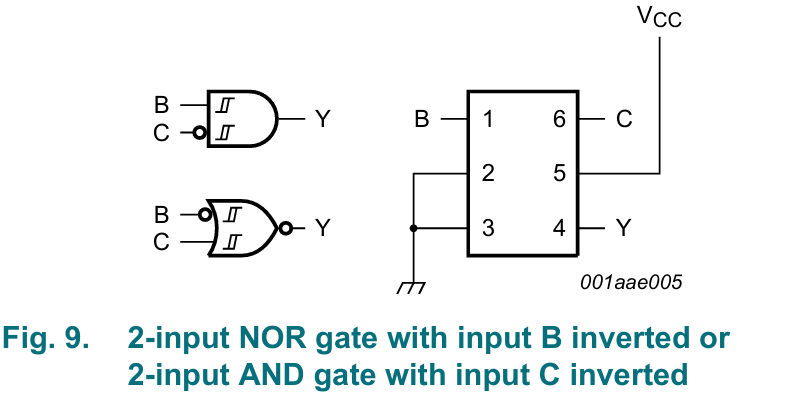

B拉高,此接法下,仅当A=!C=0时,Y=0,Y=A|~C,属于“A同相输入C反相输入的或门”(OR Gate)或“A反相输入C同相输入的与非门”(NAND Gate)接法

| B | C | A | Y |

|---|---|---|---|

| H | L | L | H |

| H | L | H | H |

| H | H | L | L |

| H | H | H | H |

A作为设置信号

A拉低,此接法下,仅当~C=B=1时,Y=1,因此,Y=B&~C,属于“B同相输入C反相输入的与门”(AND Gate)或“B反相输入C同相输入的或非门”(NOR Gate)接法

| A | C | B | Y |

|---|---|---|---|

| L | L | L | L |

| L | H | L | L |

| L | L | H | H |

| L | H | H | L |

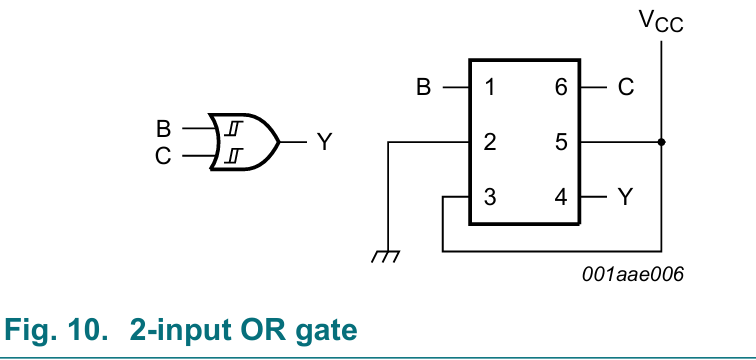

A拉高,此接法下,Y=B|C,属于“或门”(OR Gate)接法

| A | C | B | Y |

|---|---|---|---|

| H | L | L | L |

| H | H | L | H |

| H | L | H | H |

| H | H | H | H |

至此,6种逻辑门接法、1种复用器接法已经介绍完毕!

当1个输入引脚引出,2个输入引脚固定拉高或拉低时,必然工作为缓冲器或反相器,该功能较为简单,直接列举:

C=1,B=X时,Y=A,为缓冲器(2:1 Mux的特殊用法,输出Y永不选通至输入B)

C=0,A=X时,Y=B,为缓冲器(2:1 Mux的特殊用法,输出Y永不选通至输入A)

A=B=1时,Y=1,无逻辑功能(2:1 Mux的无效用法,两个选通路径均为1)

A=B=0时,Y=0,无逻辑功能(2:1 Mux的无效用法,两个选通路径均为0)

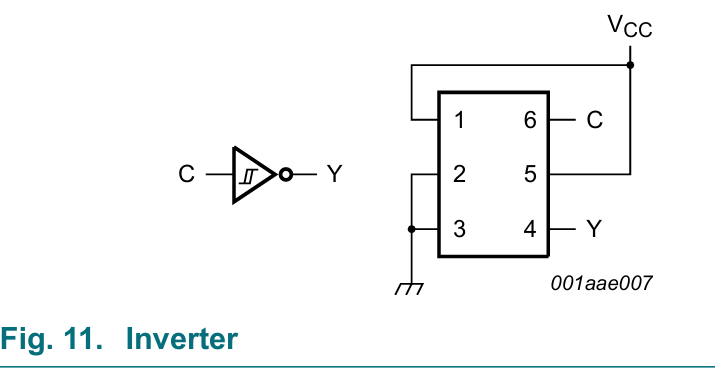

A=0,B=1时,Y=~C,为反相器(2:1 Mux的LUT用法)

A=1,B=0时,Y=C,为缓冲器(2:1 Mux的LUT用法)

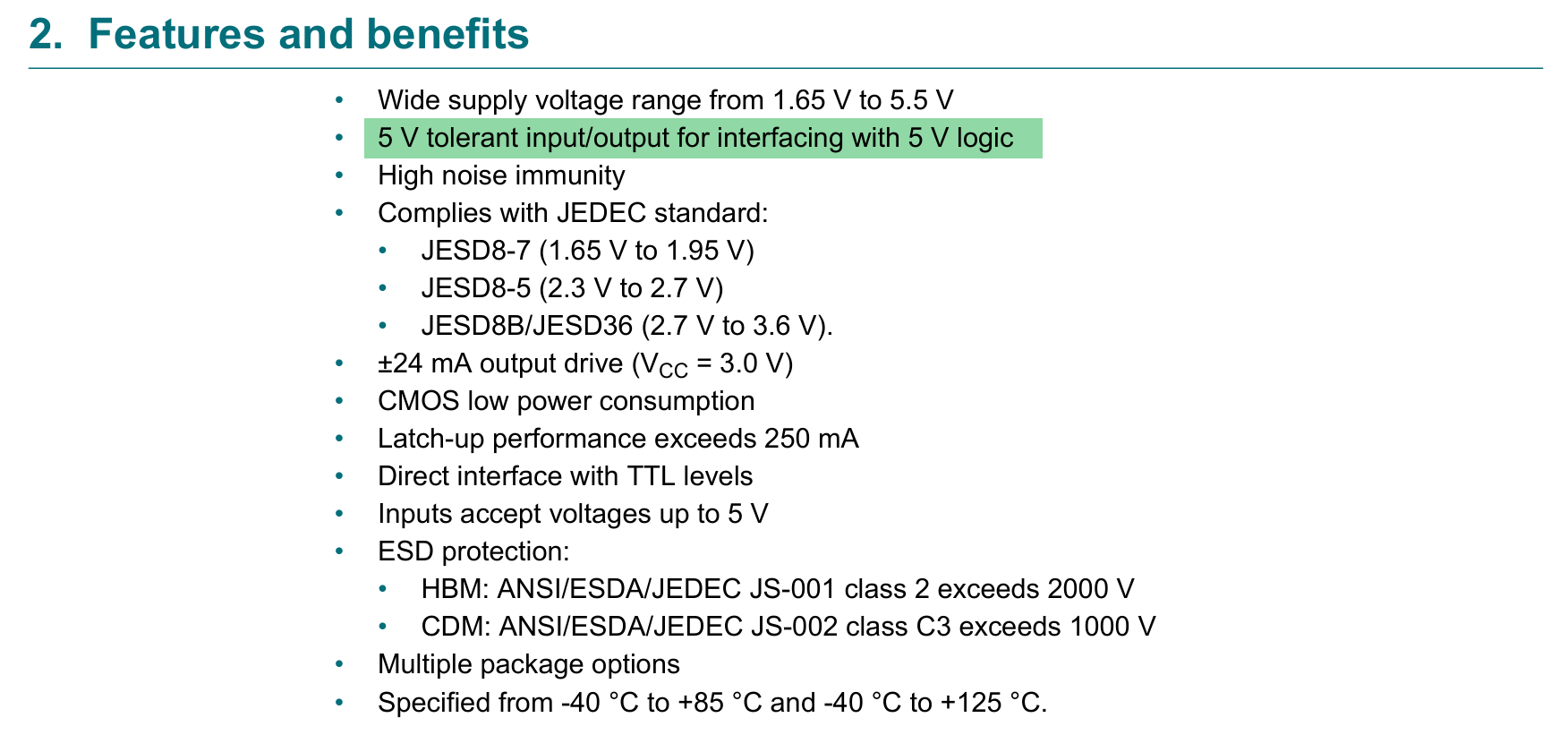

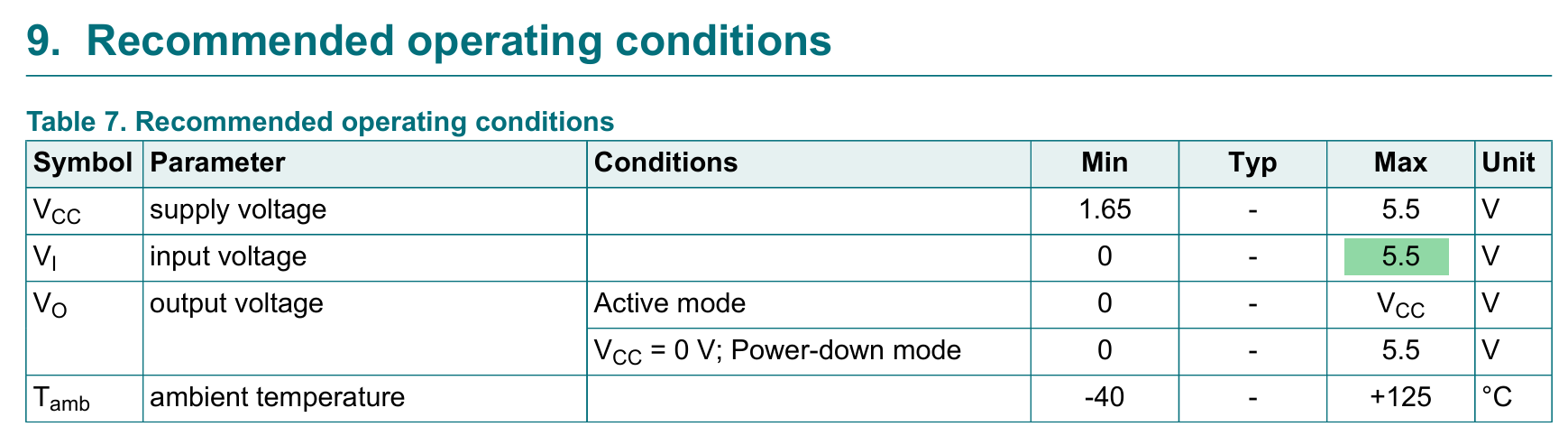

供电要求

1.65V~5.5V供电。

输入特性

所有输入端口均为5V容忍输入,允许在VCC低于5V时(例如3.3V、2.5V、1.8V供电时),使用5V电平标准的输入信号

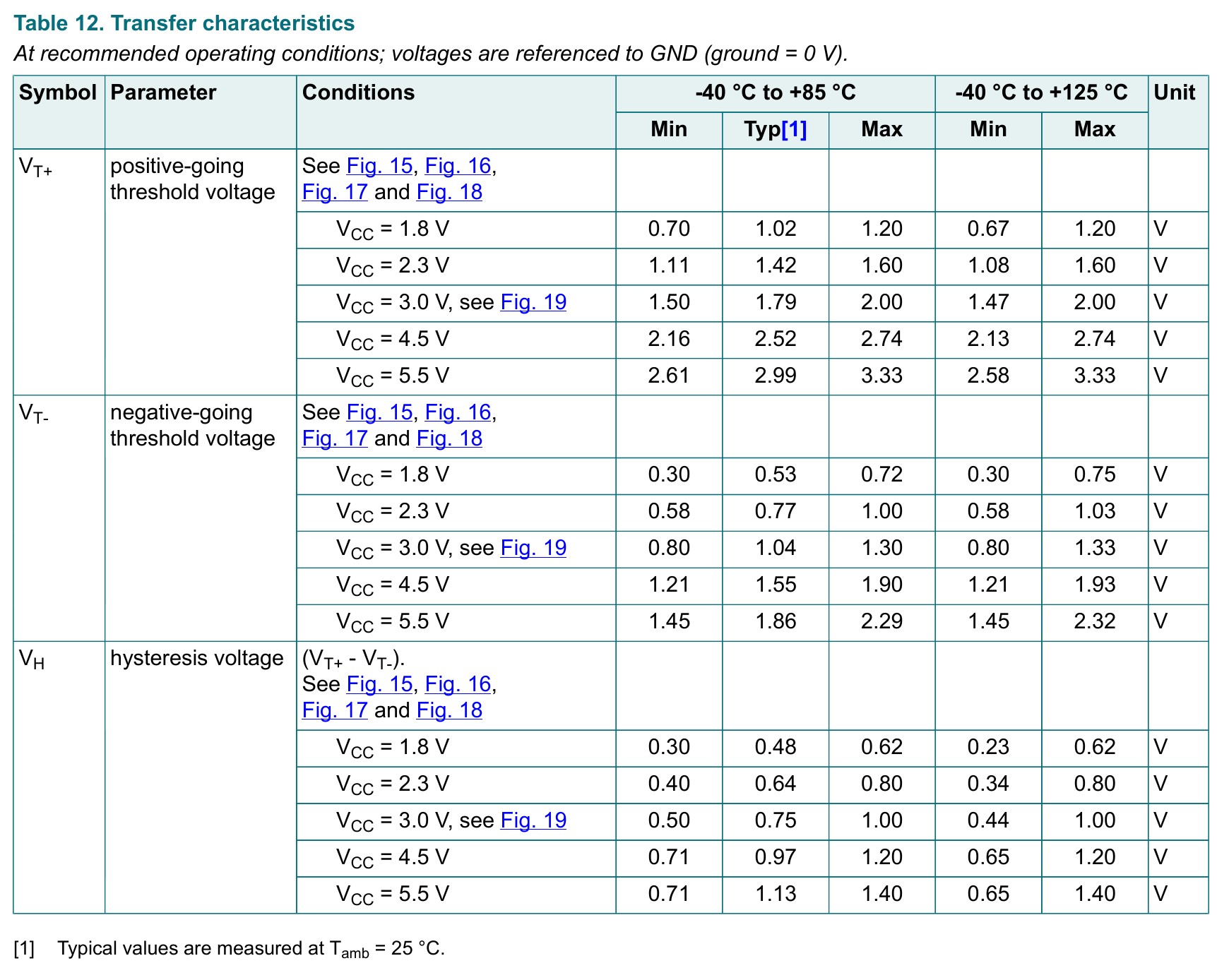

输入抗干扰能力

3个输入端口均有施密特触发器输入,可用于抑制输入噪声。在4.5V输入下,通常可以容忍0.97V的输入信号抖动。(见hysteresis voltage,VCC=4.5V,-40℃~+85℃,Typ数据)

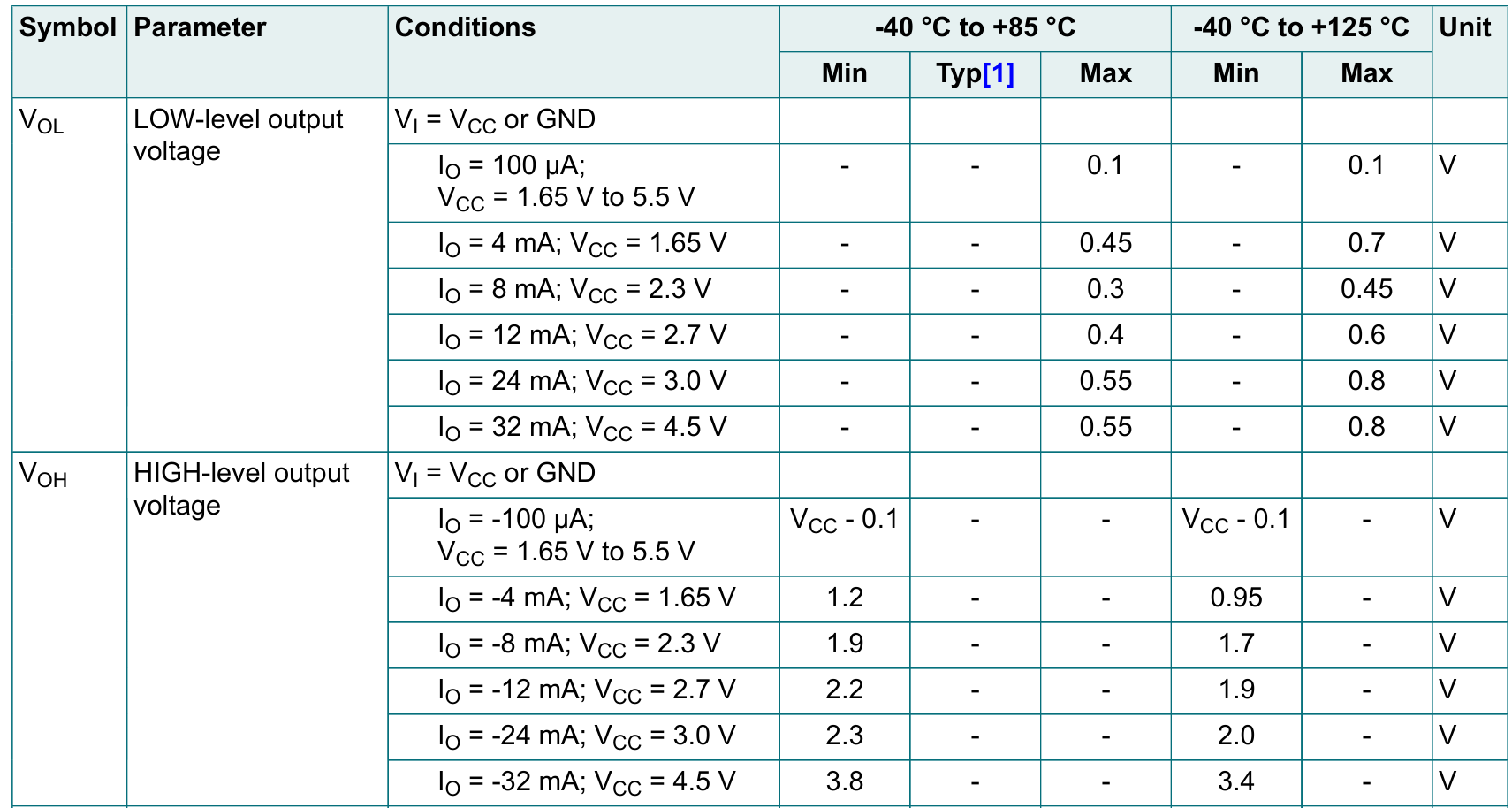

输出驱动能力

4.5V输出条件下,

输出端口可在32mA灌电流下提供低至Vo-GND=0.55V的压差;可在32mA灌电流下提供至少低至VCC-Vo=4.5-3.8=0.7V的压差,能够满足几乎所有的信号输出场景。

1G97小结

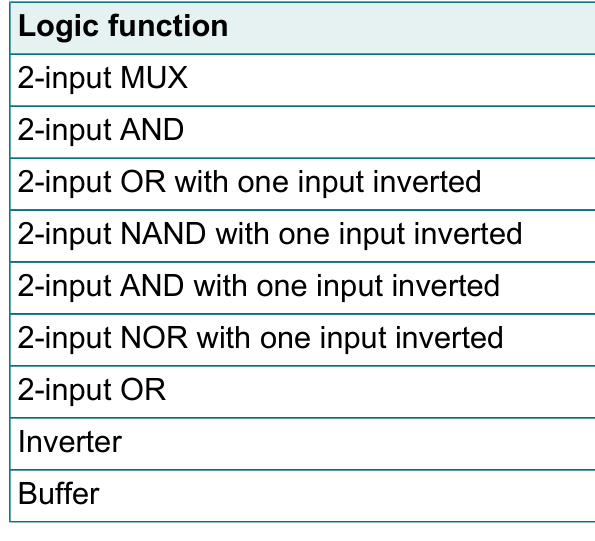

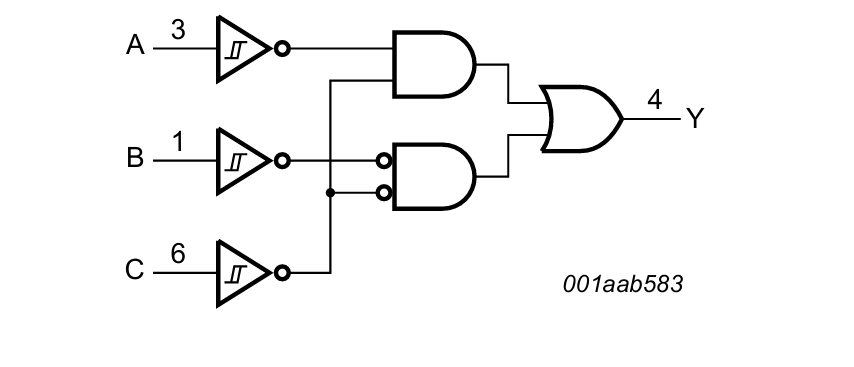

总结来说,74LVC1G97支持根据不同的连线,基于给定的真值表,实现如下9种逻辑功能:

| C | B | A | Y |

|---|---|---|---|

| L | L | L | L |

| L | L | H | L |

| L | H | L | H |

| L | H | H | H |

| H | L | L | L |

| H | L | H | H |

| H | H | L | L |

| H | H | H | H |

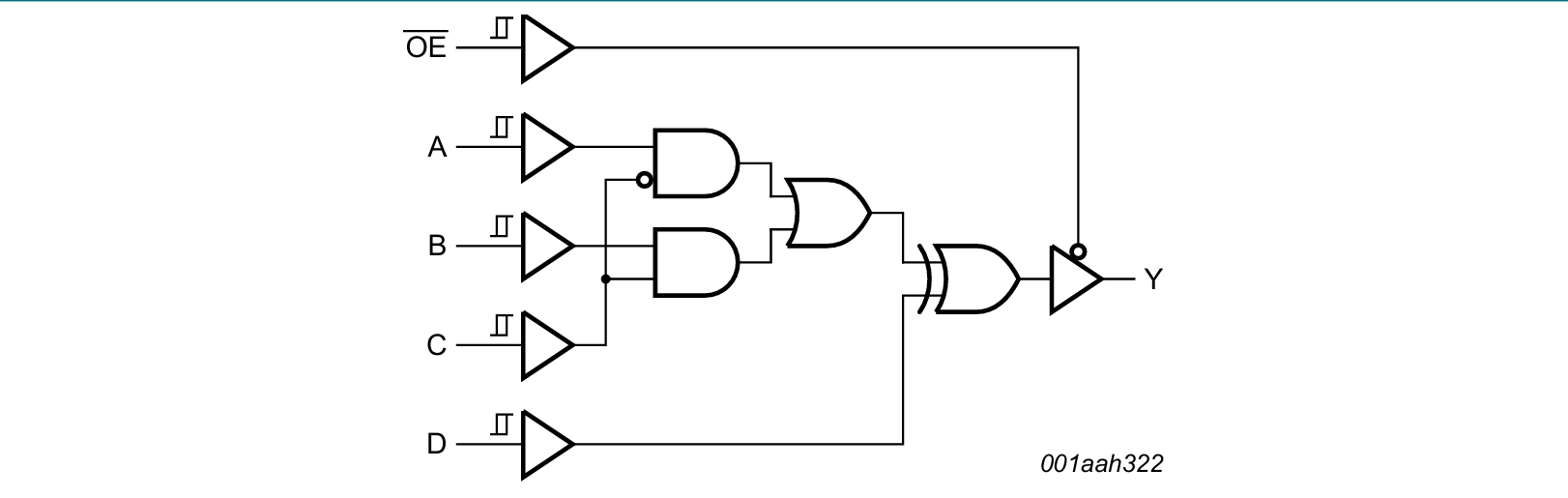

其他可编程多功能门芯片

对比同类的其他可编程多功能门芯片,真值表和功能分别如下。

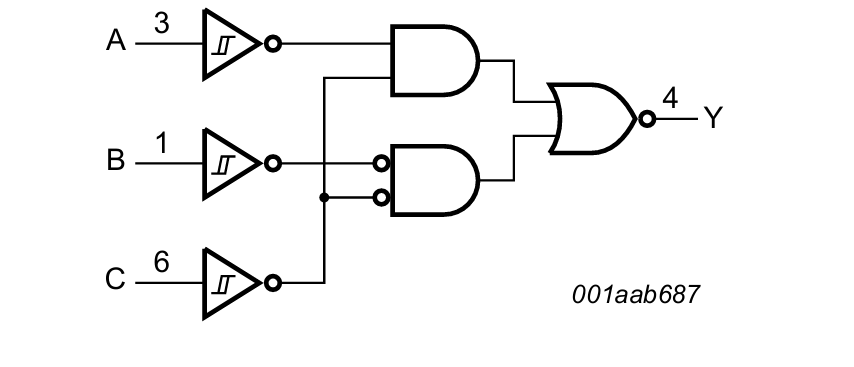

74LVC1G98

与1G97相比,仅将输出门更改为了反相输出,因此可实现的功能基本不变

| C | B | A | Y |

|---|---|---|---|

| L | L | L | H |

| L | L | H | H |

| L | H | L | L |

| L | H | H | L |

| H | L | L | H |

| H | L | H | L |

| H | H | L | H |

| H | H | H | L |

74LVC1G57

采用了与1G97和1G98完全不同的逻辑门结构,支持的功能也不同了。

| C | B | A | Y |

|---|---|---|---|

| L | L | L | H |

| L | L | H | L |

| L | H | L | H |

| L | H | H | L |

| H | L | L | L |

| H | L | H | L |

| H | H | L | H |

| H | H | H | H |

74LVC1G58

与1G57相比,仅将输出门更改为了反相输出,因此可实现的功能基本不变

| C | B | A | Y |

|---|---|---|---|

| L | L | L | L |

| L | L | H | H |

| L | H | L | L |

| L | H | H | H |

| H | L | L | H |

| H | L | H | H |

| H | H | L | L |

| H | H | H | L |

74LVC1G99

这是一款厉害的8引脚的逻辑芯片,有4个输入引脚和1个输出引脚。可以实现1G97、1G98、1G57、1G58任何一款芯片的功能。同时具有额外的OE引脚,可以实现三态输出(OE=1时,输出为高阻态,既不输出低电平,也不输出高电平)

| D | C | B | A | Y |

|---|---|---|---|---|

| L | L | L | L | L |

| L | L | L | H | H |

| L | L | H | L | L |

| L | L | H | H | H |

| L | H | L | L | L |

| L | H | L | H | L |

| L | H | H | L | H |

| L | H | H | H | H |

| H | L | L | L | H |

| H | L | L | H | L |

| H | L | H | L | H |

| H | L | H | H | L |

| H | H | L | L | H |

| H | H | L | H | H |

| H | H | H | L | L |

| H | H | H | H | L |

总结

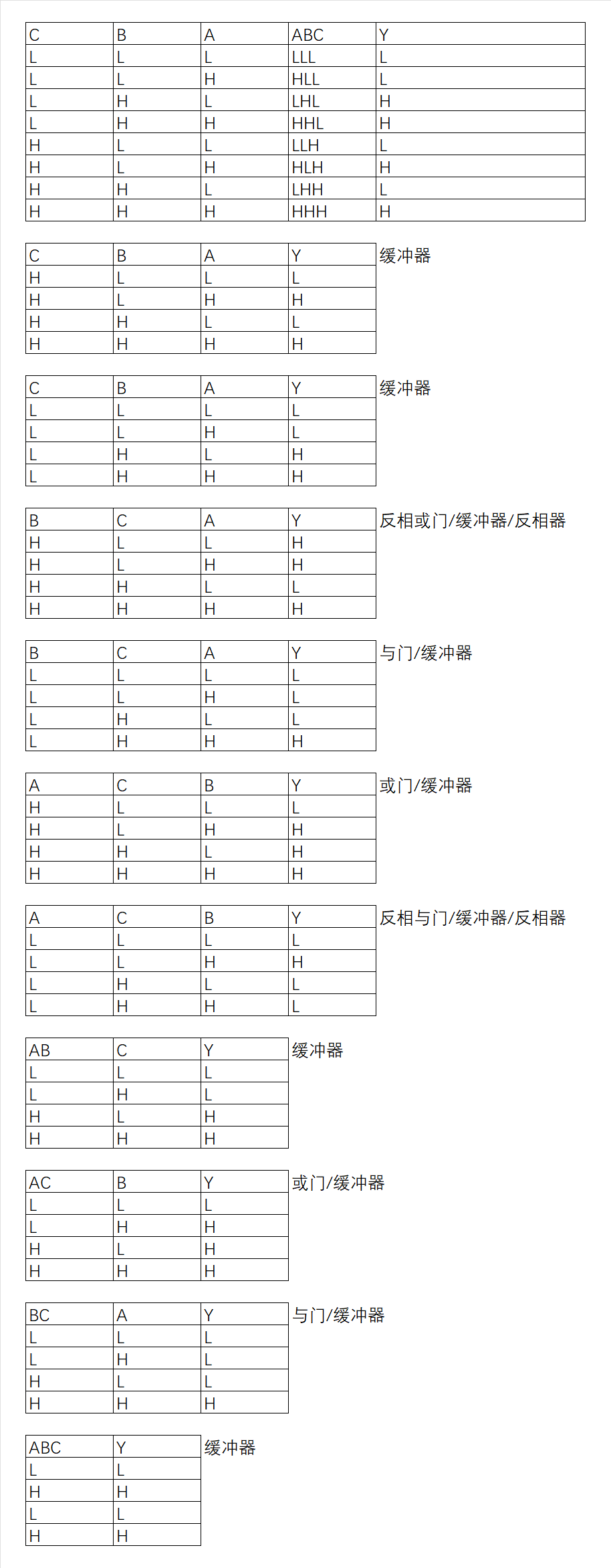

1G97、1G98、1G57、1G58、1G99这5款可编程多功能门芯片对12种逻辑输出功能的支持情况如下表。

其中1G97、1G98只支持其中7种功能,1G57、1G58只支持其中6种功能,1G99支持全部12种功能。

| 功能 | 等效功能 | 1G97 | 1G98 | 1G57 | 1G58 | 1G99 |

|---|---|---|---|---|---|---|

| 2输入复用器 | √ | × | × | × | √ | |

| 2输入复用器(反相输出) | × | √ | × | × | √ | |

| 2输入与门(AND Gate当输入全为1时输出1) | 全反相输入的或非门 | √ | × | √ | × | √ |

| 2输入或门(OR Gate当输入全为0时输出0) | 全反相输入的与非门 | √ | × | × | √ | √ |

| 2输入或非门(NOR Gate是反相输出的或门) | 全反相输入的与门 | × | √ | √ | × | √ |

| 2输入与非门(NAND Gate是反相输出的与门) | 全反相输入的或门 | × | √ | × | √ | √ |

| 2输入同或门(XNOR Gate当2个输入相同时输出1) | 带1个反相输入或反相输出的异或门 | × | × | √ | × | √ |

| 2输入异或门(XOR Gate当2个输入不同时输出1) | 带1个反相输入或反相输出的同或门 | × | × | × | √ | √ |

| 带1个反相输入的2输入或门 | 带1个反相输入的2输入与非门 | √ | √ | √ | × | √ |

| 带1个反相输入的2输入与门 | 带1个反相输入的2输入或非门 | √ | √ | × | √ | √ |

| 反相器 | √ | √ | √ | √ | √ | |

| 缓冲器 | √ | √ | √ | √ | √ |

附录

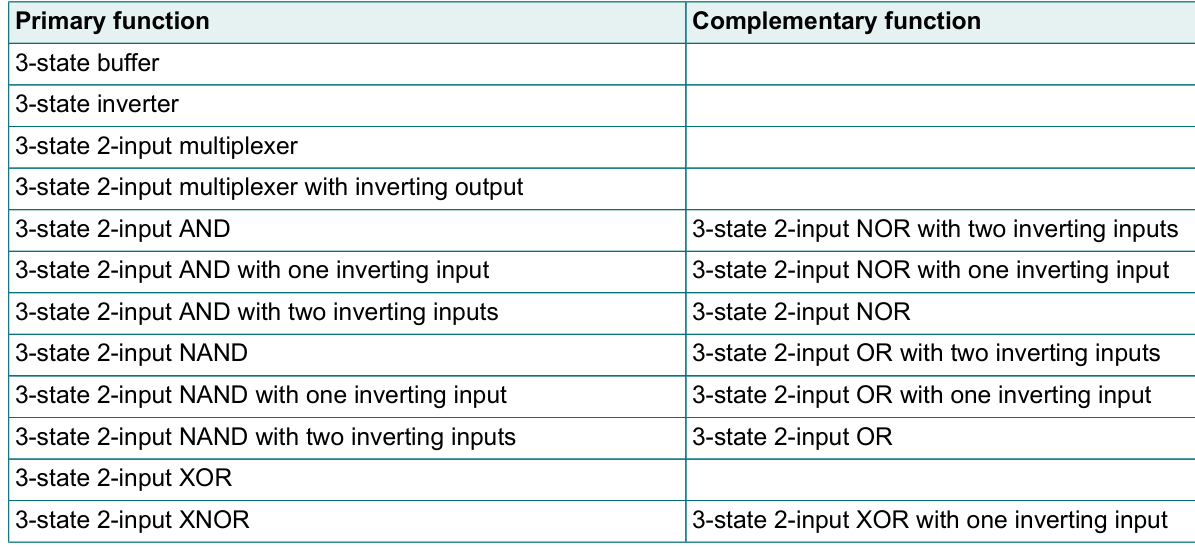

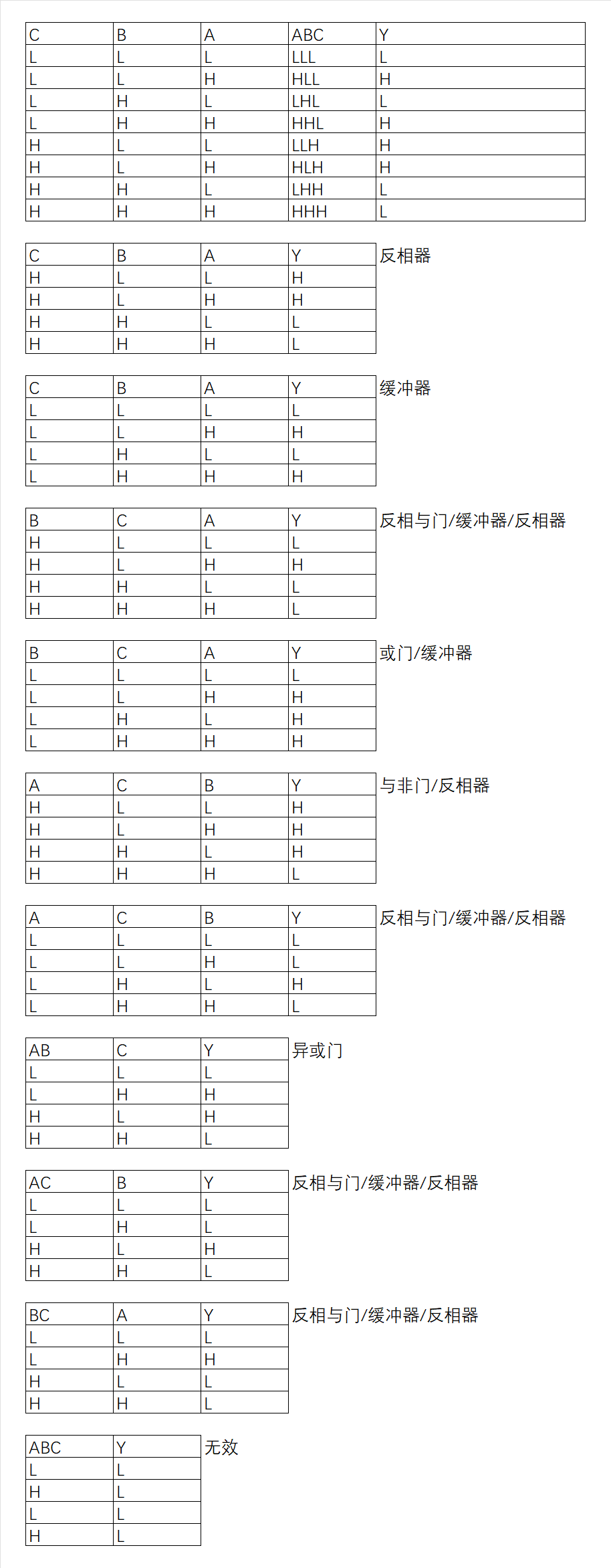

1G97各种模式的详细真值表

1G58各种模式的详细真值表

备注

本文中与74LVC1G97有关的截图,均引用自Nexperia 74LVC1G97 Datasheet Rev. 8.1,2023年8月更新

本文中与74LVC1G98有关的截图,均引用自Nexperia 74LVC1G98 Datasheet Rev. 7.1,2023年8月更新

本文中与74LVC1G57有关的截图,均引用自Nexperia 74LVC1G57 Datasheet Rev. 11,2023年8月更新

本文中与74LVC1G58有关的截图,均引用自Nexperia 74LVC1G58 Datasheet Rev. 12,2023年8月更新

本文中与74LVC1G99有关的截图,均引用自Nexperia 74LVC1G99 Datasheet Rev. 13,2024年8月更新

上述数据手册截至2025年4月,仍为最新版本