ZYNQ笔记(一):hello world

版本:Vivado2020.2(Vitis)

任务:配置ZYNQ 及其 UART,串口打印 hello world

目录

一、ZYNQ 介绍

二、开发流程

三、硬件设计

四、软件设计

五、效果

一、ZYNQ 介绍

ZYNQ 是赛灵思(Xilinx)公司推出的全可编程片上系统(All Programmable SoC),它将双核ARM Cortex-A9处理器与 Xilinx 7系列FPGA架构紧密集成在单一芯片上。

ZYNQ 主要由两大子系统构成:

-

处理系统(PS - Processing System)

-

双核ARM Cortex-A9 MPCore处理器(最高1GHz)

-

丰富的外设接口(DDR控制器、USB、UART、SPI、I2C等)

-

存储器接口(支持DDR2/DDR3/LPDDR2)

-

通用外设控制器

-

-

可编程逻辑(PL - Programmable Logic)

-

基于Xilinx 7系列FPGA架构

-

可配置逻辑块(CLB)、DSP切片、Block RAM

-

可编程I/O

-

关键特性

-

高性能处理+灵活可编程:ARM处理器处理复杂算法,FPGA实现高速并行处理

-

AXI互联:PS与PL通过多种AXI接口高速通信(包括GP、HP、ACP接口)

-

低功耗设计:适合嵌入式应用

-

丰富外设:集成常用外设控制器,减少外围电路

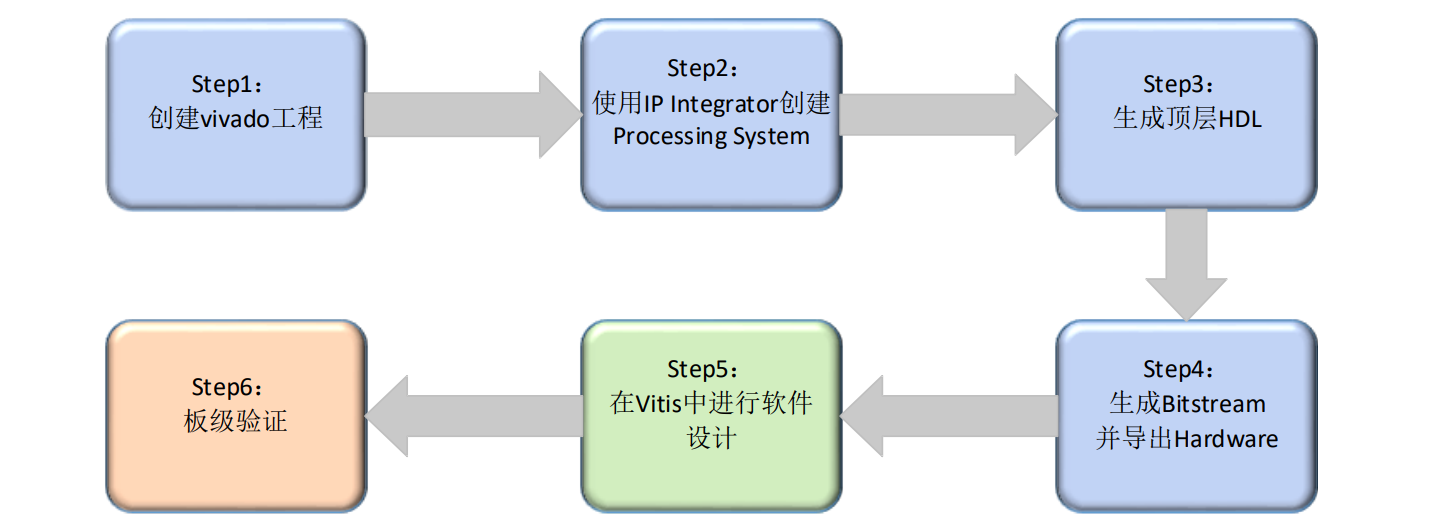

二、开发流程

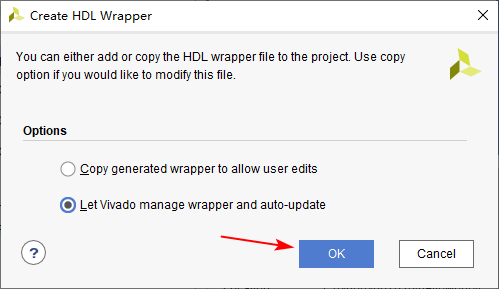

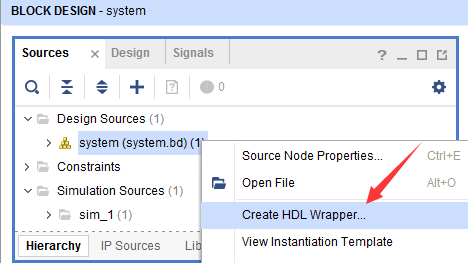

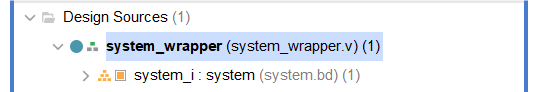

ZYNQ开发流程分为软硬件两个部分。硬件部分包括:BD设计、配置IP、约束管脚、生成比特流文件;软件部分就是Vitis/SDK中进行软件设计。设计检查无误后,接着Create HDL Wrapper、管脚约束(PL端KEY、LED)、Gnerate Bitstream、Export Hardware(包含比特流文件)、启动Vitis/SDK

三、硬件设计

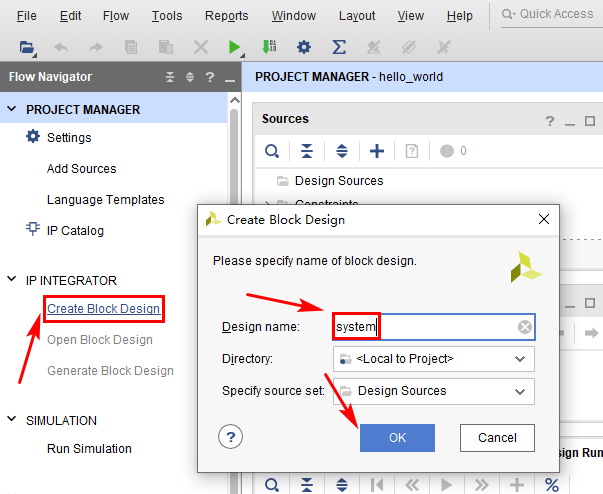

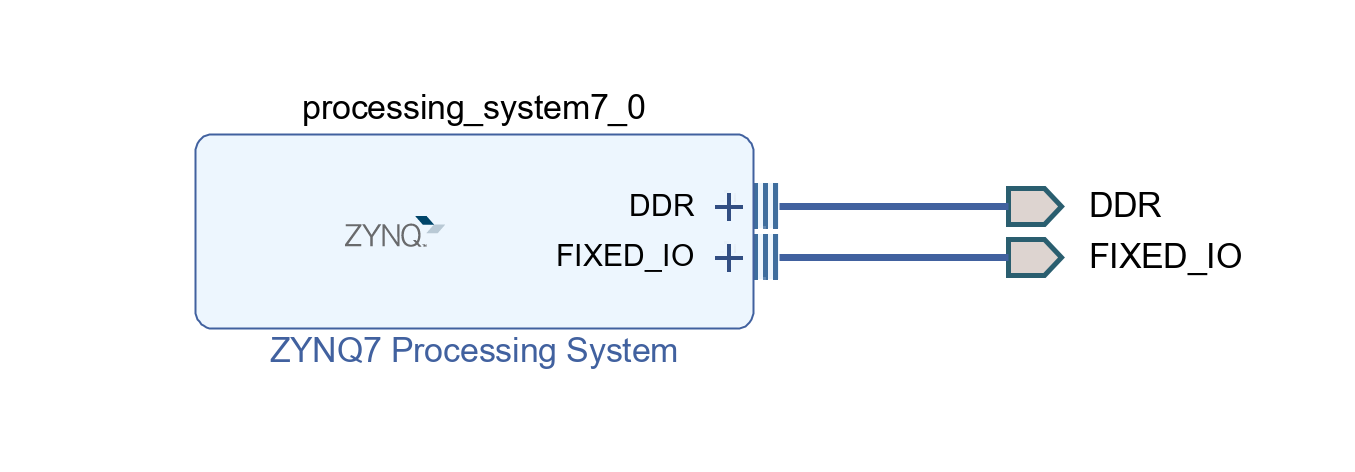

(1)新建工程后创建 BlockDesign(bd设计),取名为system

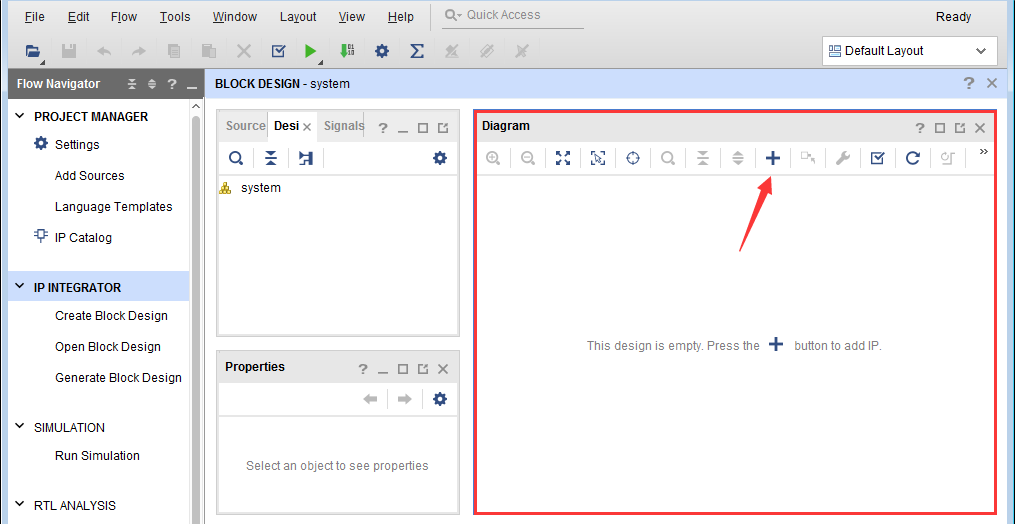

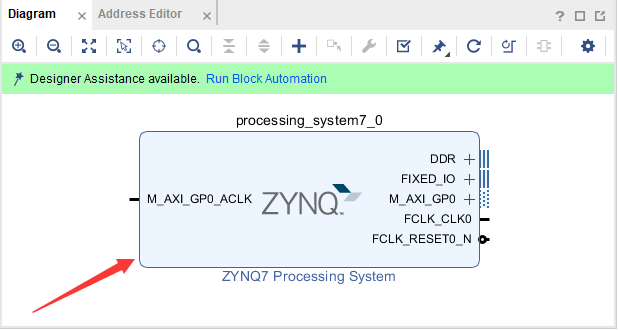

(2) 添加 ZYNQ IP

(3)双击进行 ZYNQ 配置

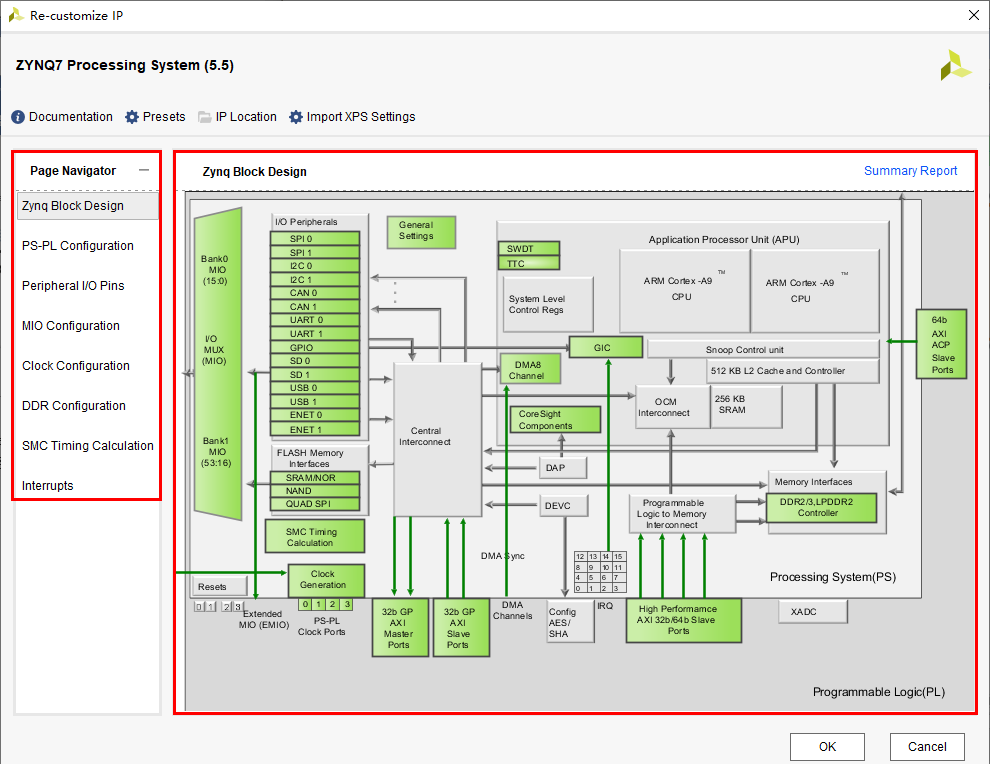

(4)配置界面如图:左侧分别为块设计、PS-PL配置、外设IO引脚、MIO配置、时钟配置、DDR配置(系统的运行需要存储器的支持,一般选择使用外挂的 DDR3 芯片,因此需要用到 PS 中的 DDR3 控制器)、SMC 时序计算、中断。每个部分配置过程不再赘述,用什么就相应取配置,没有使用到的可以配置去掉,详细操作参考了B站正点原子的视频。

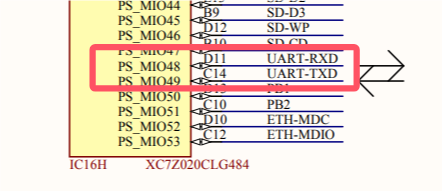

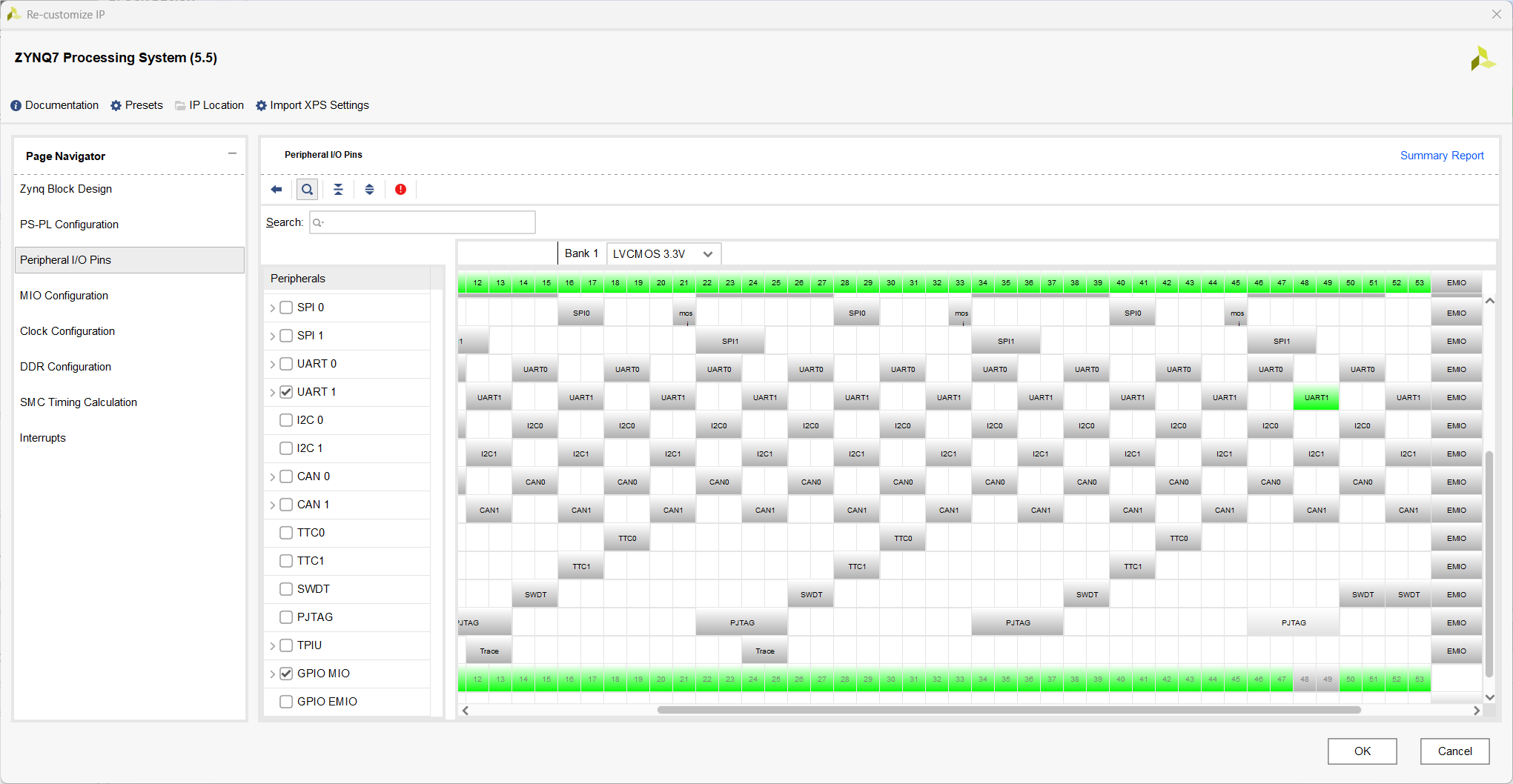

(5)串口打印需要配置UART,结合自己开发板的引脚进行配置,我的开发板原理图显示UART接口在 GPIO MIO 48、49引脚上,因此配置需要选对应的管脚。

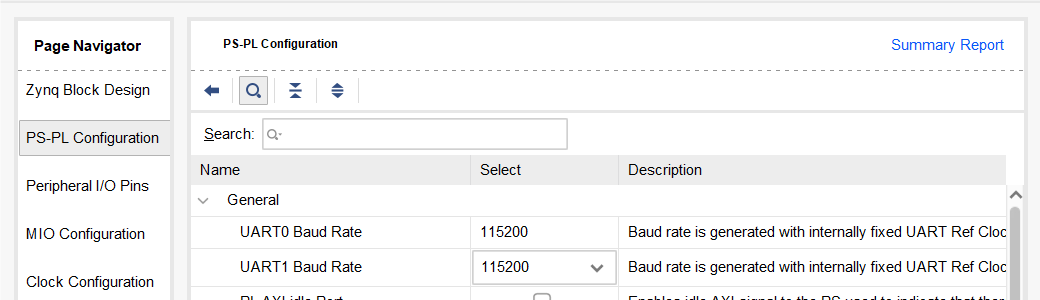

此外UART默认波特率115200,这里不作修改

(3)最后整体bd设计部分如图所示:接下来按照步骤操作

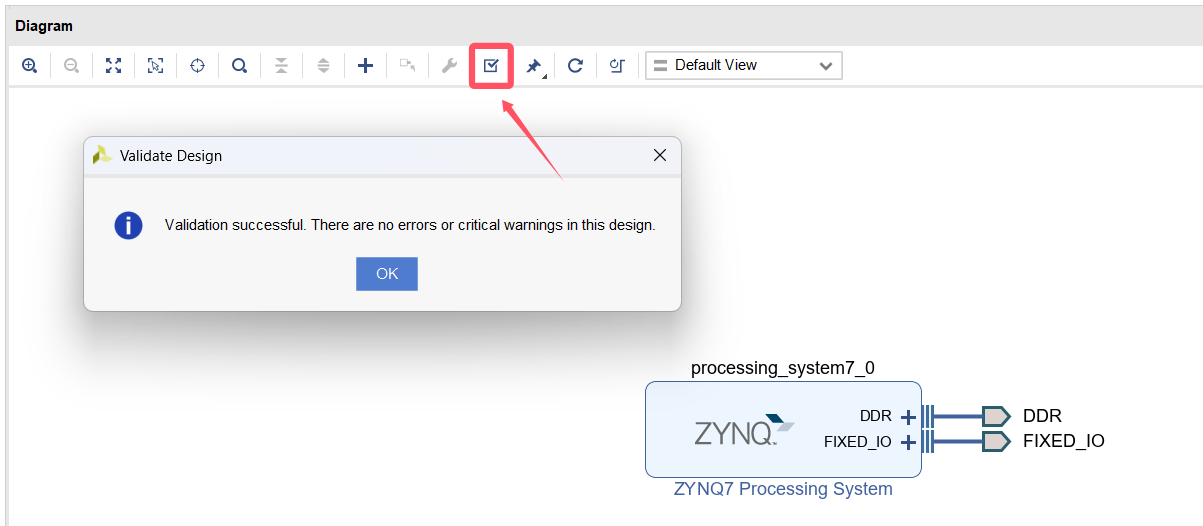

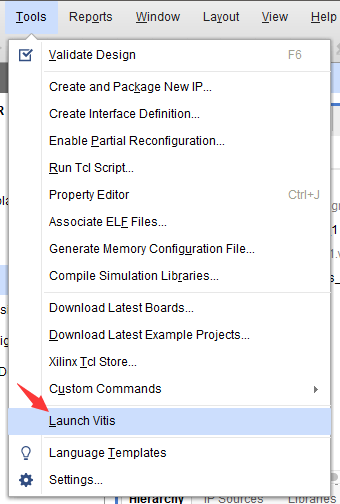

1.“Validate Design”:检查设计连接是否有误,无误后继续下一步

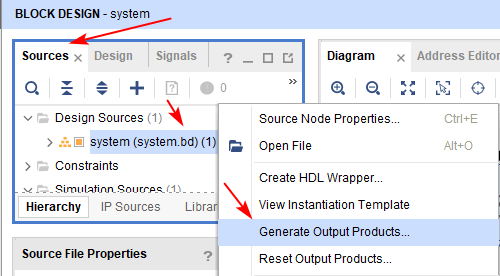

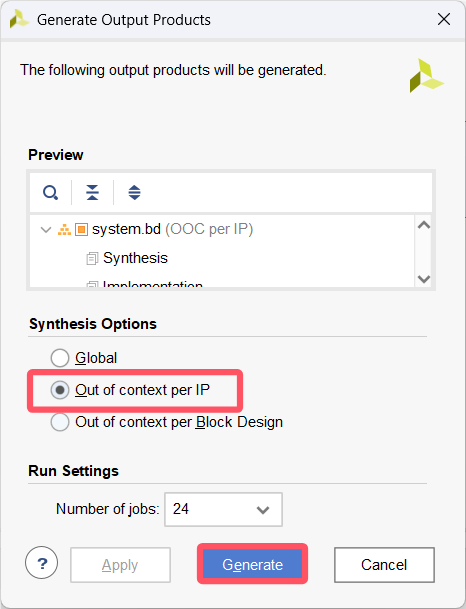

2. “Generate Output Products”:在“Generate”过程中会为设计生成所有需要的输出结果。比如 Vivado 工具会自动生成处理系统的 XDC 约束文件,因此我们不需要手动对 ZYNQ PS 引出的接口(DDR 和 FIXED_IO)进行管脚分配。

3.“Create HDL Wrapper”:(创建HDL包装文件)用于将Vivado等工具生成的Block Design(图形化设计)自动转换为可综合的HDL代码(Verilog或VHDL)

4.管脚约束、Gnerate Bitstream ,这两步跳过,因为没有使用到PL端的资源,纯PS端实现,如果用到了PL端资源(如EMIO)或使用了PL端资源的IP核(AXI GPIO)就需要这两步。

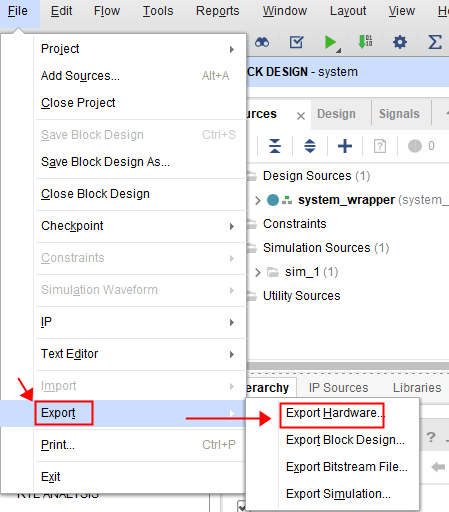

5.Export Hardware(不用包含比特流文件,因为没有)、然后启动Vitis

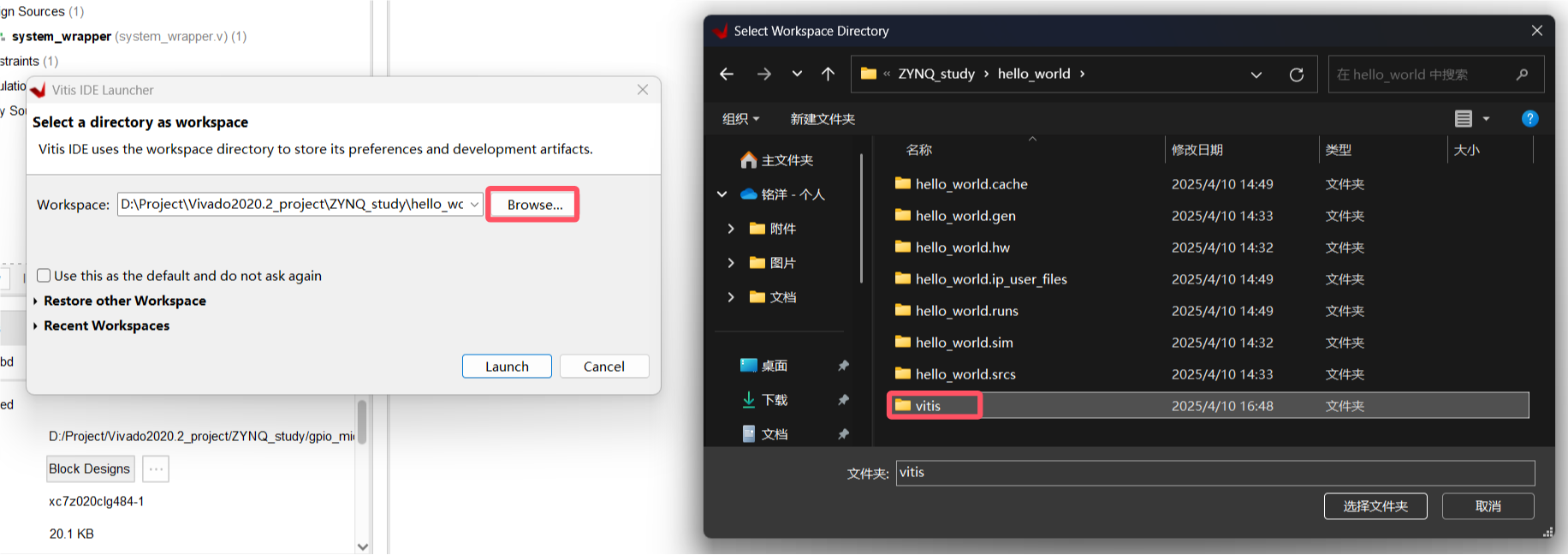

6.在工程目录下新建一个vitis文件夹存放Vitis工程,方便查找

四、软件设计

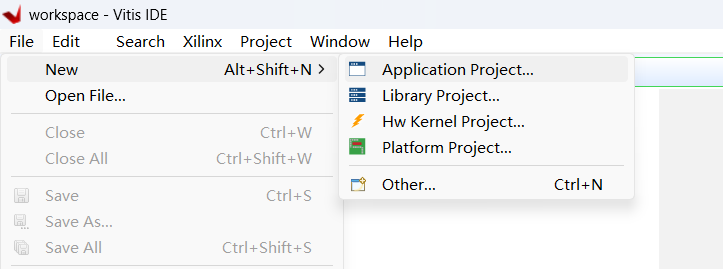

(1)进入Vitis后,新建应用工程

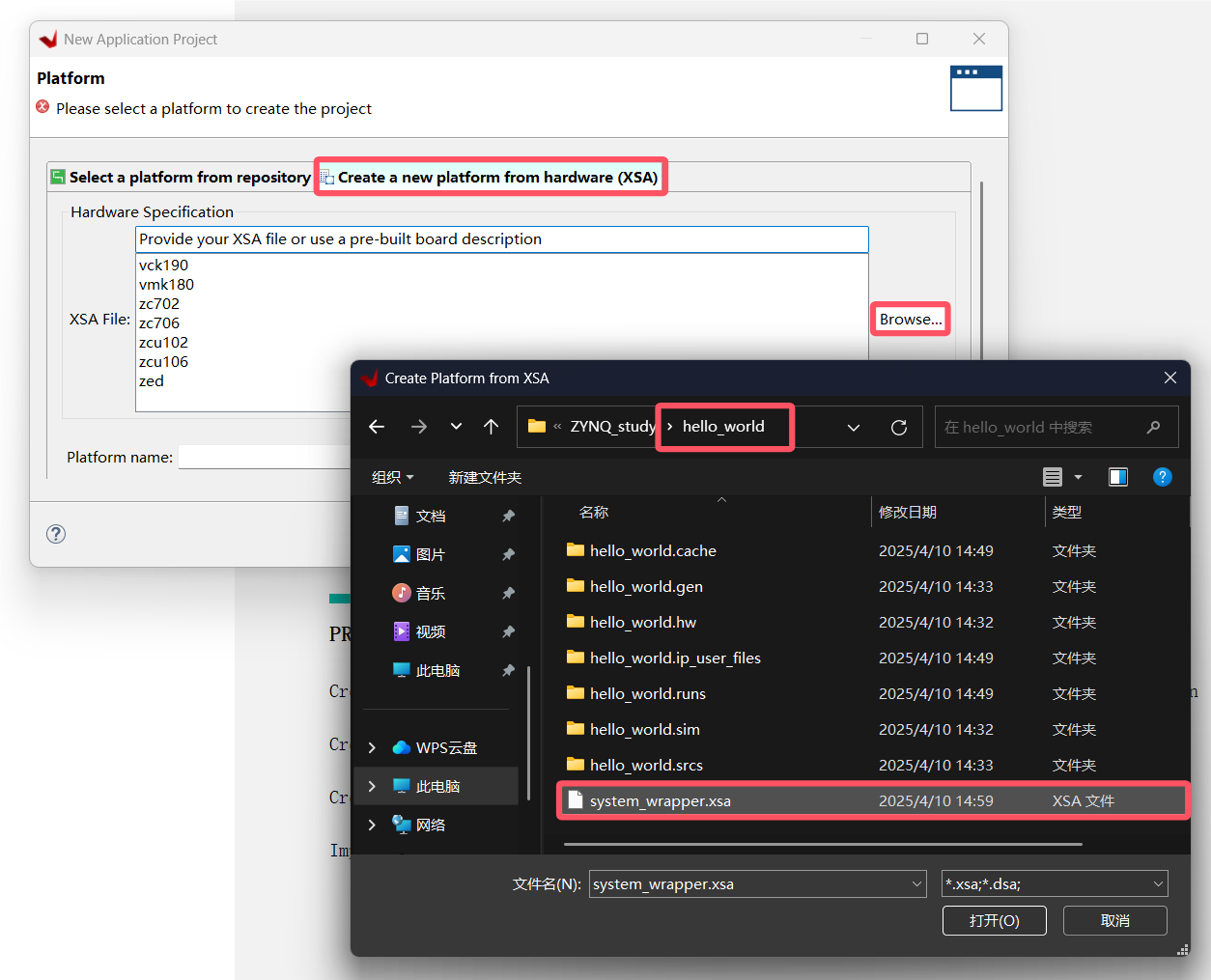

(2)打开 Create a new platform from hardware(XSA)标签页,点击“Browse”添加 xsa 文件,如下图所示:注意xsa文件到工程存放路径里去找。

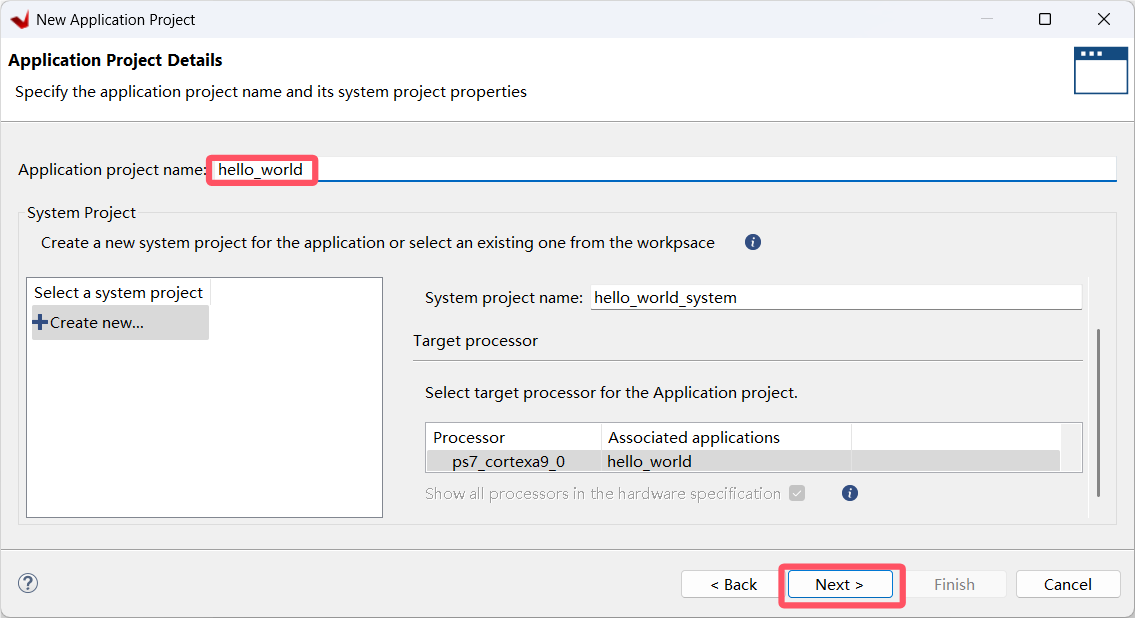

(3)应用工程命名,next

(4)选择工程模板,这里直接选空模板(也可以选已有示例)

![]()

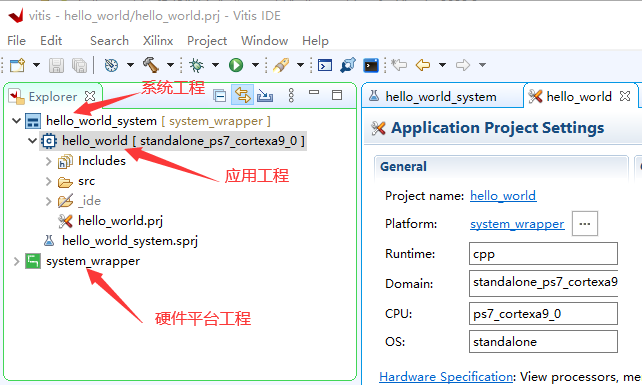

(5)工程建立完成后的页面如下图所示,可以看到生成了三个工程,一个是硬件平台工程,即 platform 工 程,一个是应用工程 hello_world,一个是系统工程 hello_world_system。系统工程可以理解为一个容器,里 面可以包含一个或多个应用工程。

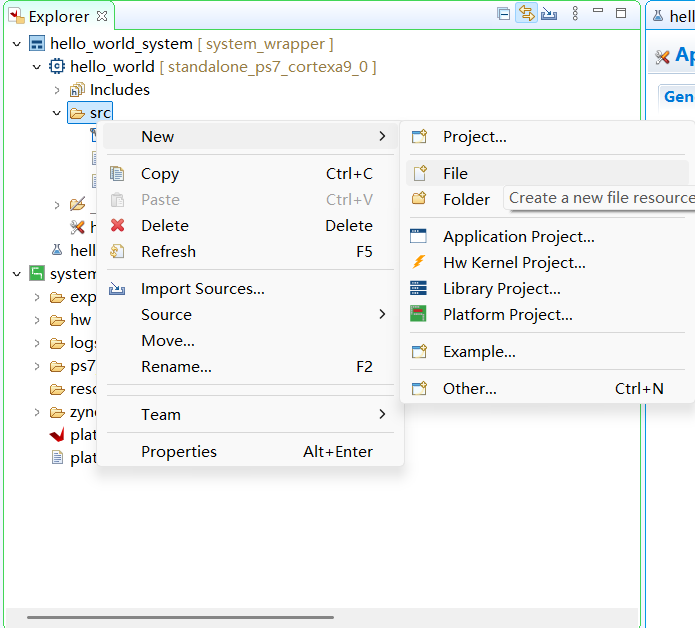

(6)新建源文件main.c

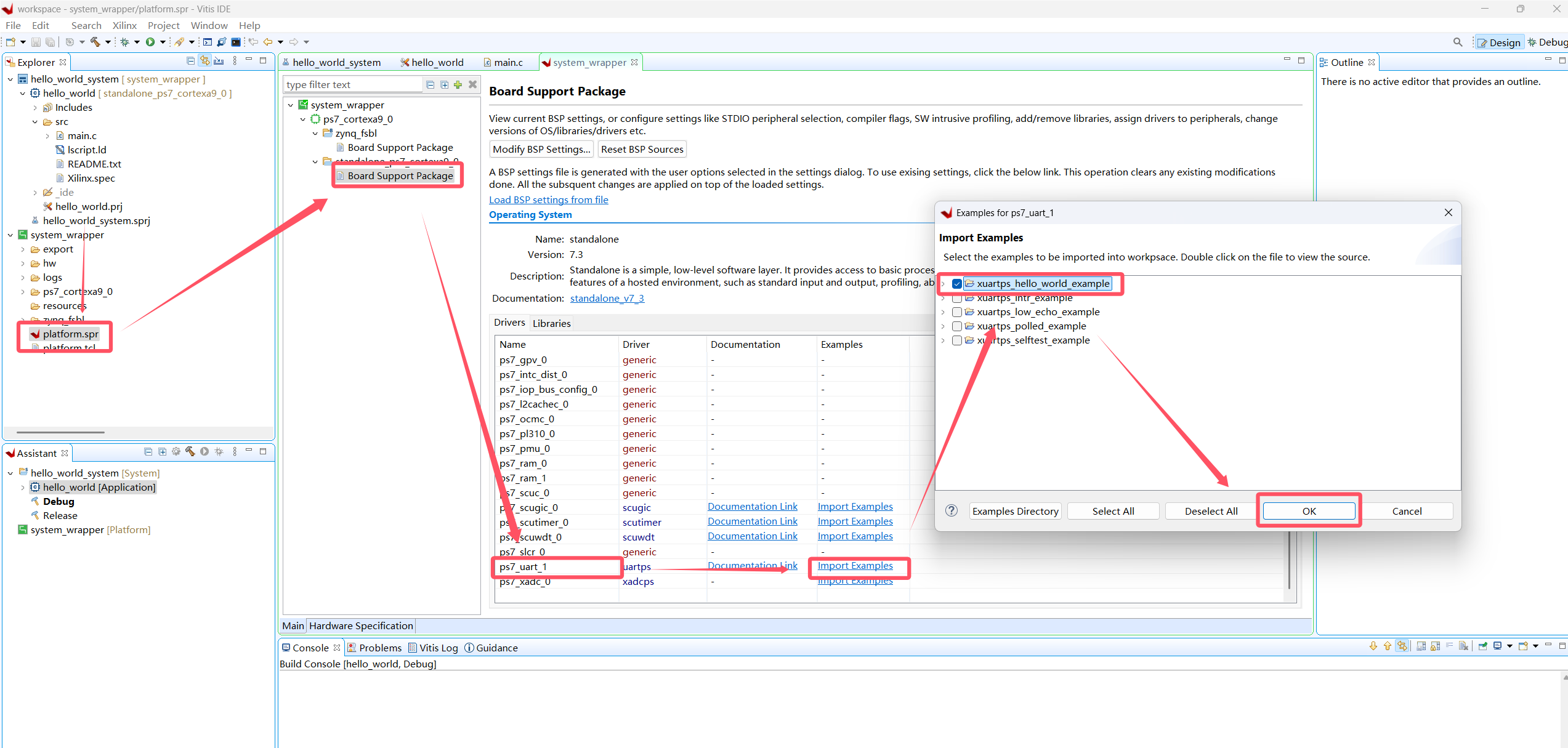

(7)双击硬件平台目录下的 platform.spr 文件,找到板级支持包“Board_Support_Package”,右侧有相关文档和示例,如下图所示:比如查看ps端uart1串口示例,点击import,选择hello world示例,。在软件中按住CTRL+左键,选择函数或变量跳转定义。同时结合官方示例代码对照编写,这样效率更高。

(7)双击硬件平台目录下的 platform.spr 文件,找到板级支持包“Board_Support_Package”,右侧有相关文档和示例,如下图所示:比如查看ps端uart1串口示例,点击import,选择hello world示例,。在软件中按住CTRL+左键,选择函数或变量跳转定义。同时结合官方示例代码对照编写,这样效率更高。

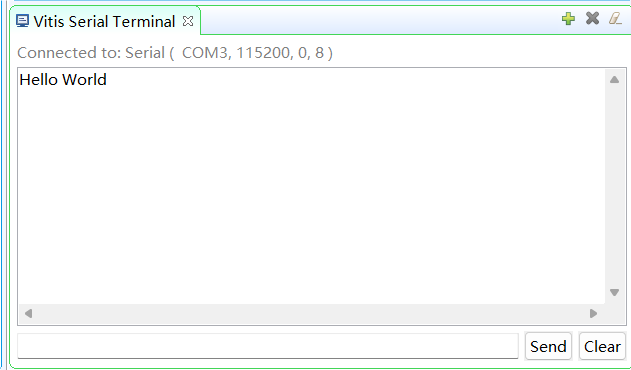

(8)代码设计:注意程序中打印字符串“Hello World”使用的是 xil_printf()函数,而不是 C 语言里的 printf()函数。 xil_printf()函数是 Xilinx 定义的一个用于打印字符串的函数,调用该函数需要包含头文件“xil_printf.h”。

#include "stdio.h"

#include "xil_printf.h"int main()

{xil_printf("Hello World\n\r");return 0;

}

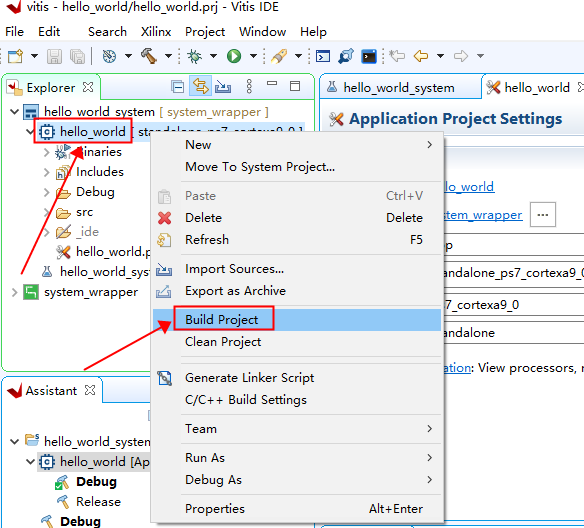

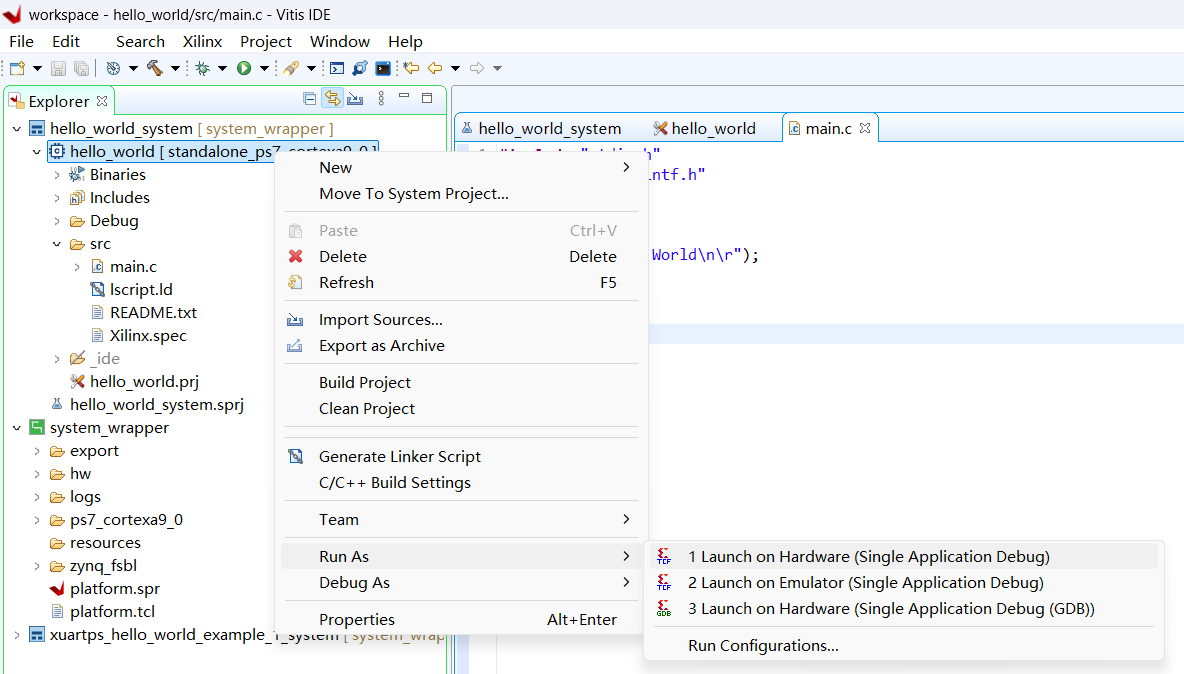

(9)编写完成后ctrl+s保存,右键工程进行编译,在下方Problems显示报错,无错误后右键Run As,点击Launch Hardware 上版运行。

五、效果

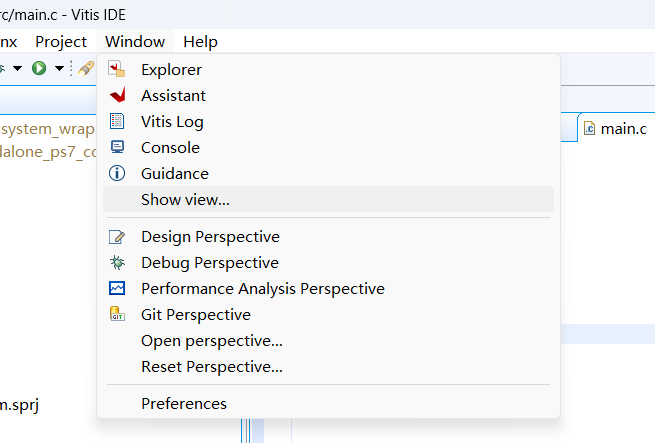

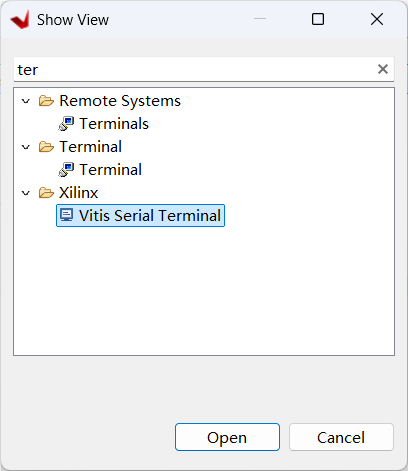

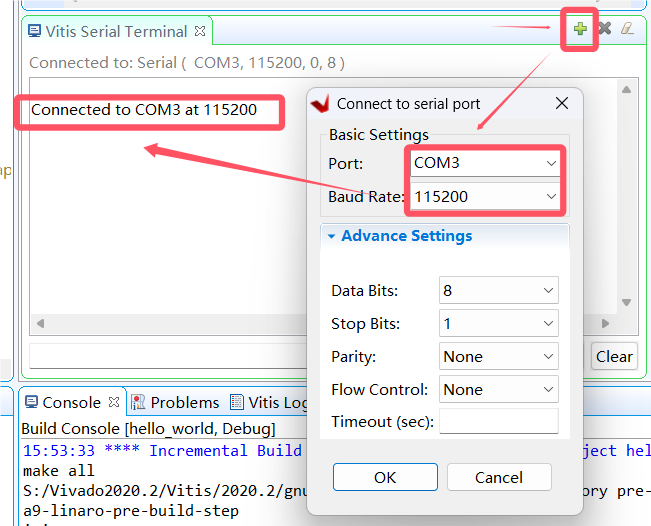

Vitis自带一个串口工具,工具栏点击Wndows、Show view,搜索Vitis Serial Terminal。

注意先连接上串口后,再运行,同时注意波特率正确,最终效果如下:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.mrgr.cn/news/98020.html 如若内容造成侵权/违法违规/事实不符,请联系邮箱:809451989@qq.com进行投诉反馈,一经查实,立即删除!