IntelliJ IDEA下开发FPGA——FPGA开发体验提升__上

前言

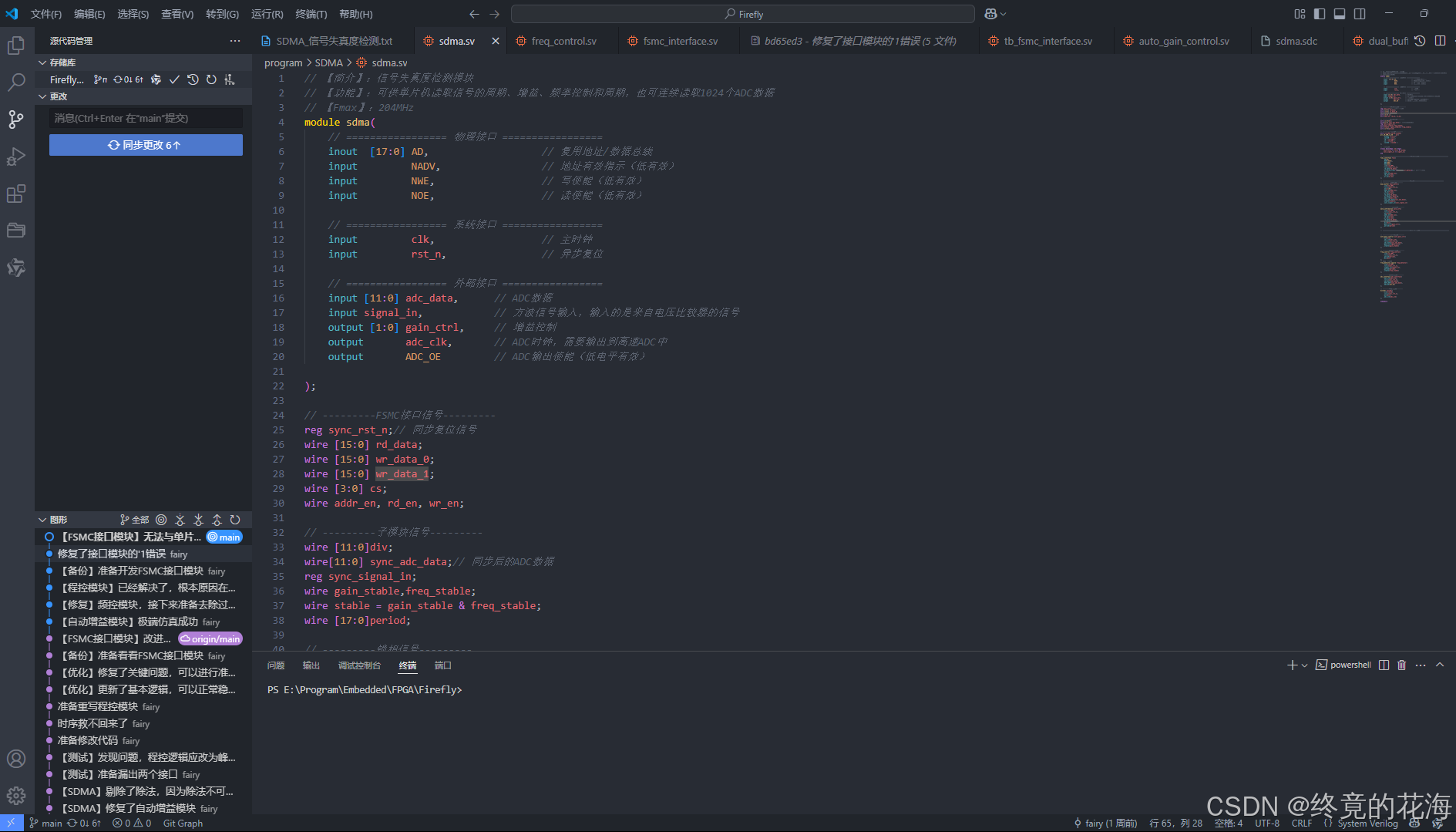

由于Quartus写代码比较费劲,虽然新版已经有了代码补全,但体验上还有所欠缺。于是使用VS Code开发,效果如下所示,代码样式和基本的代码补全已经可以满足开发,其余工作则交由Quartus完成

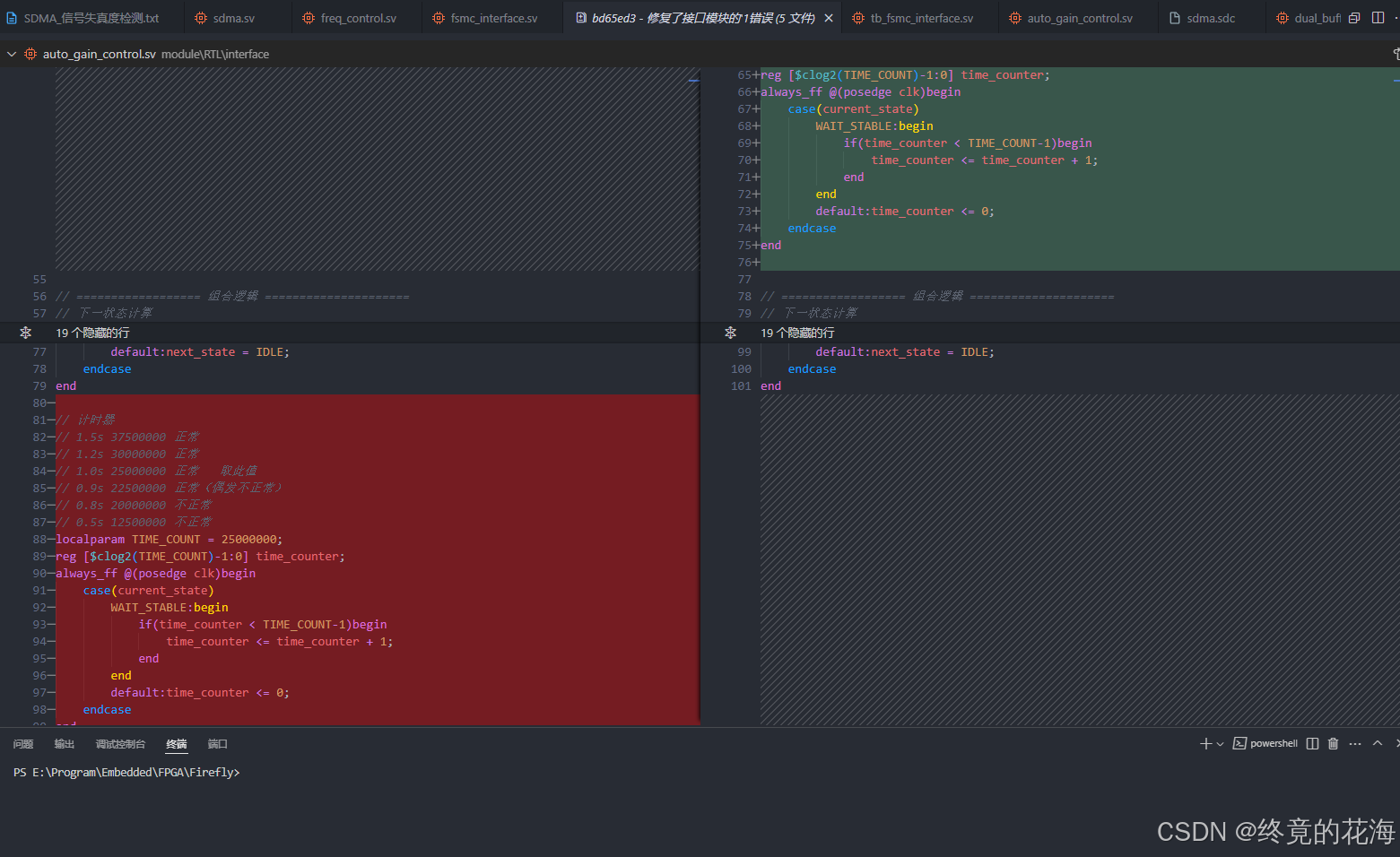

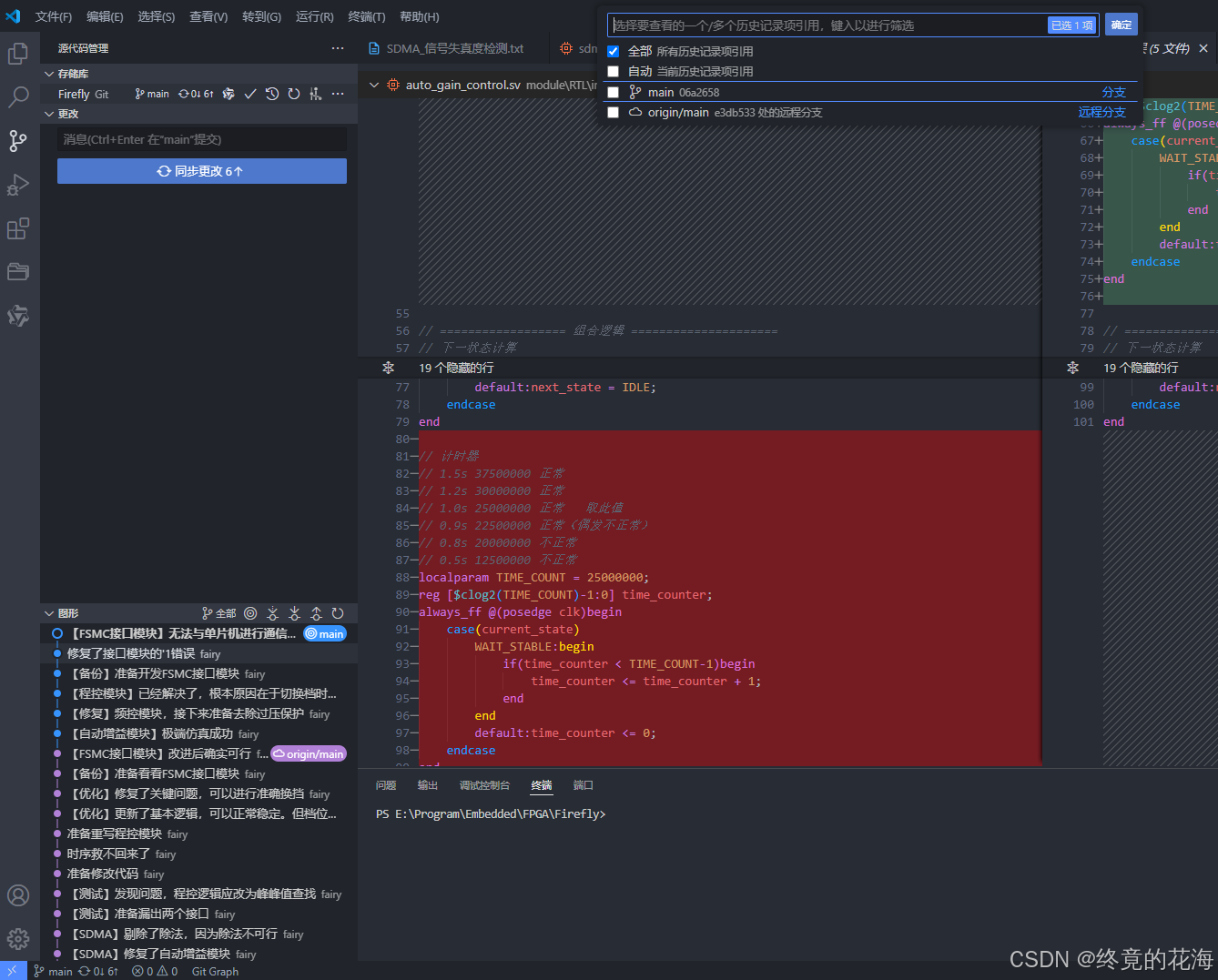

但VS Code的自带的git功能,说实话并不好用,只能查看更改的,需要手动展开才能浏览全局代码。而合并过程,辨识度并不是很高,容易造成重复代码

分支方面并不清晰,虽然提供了多种视图

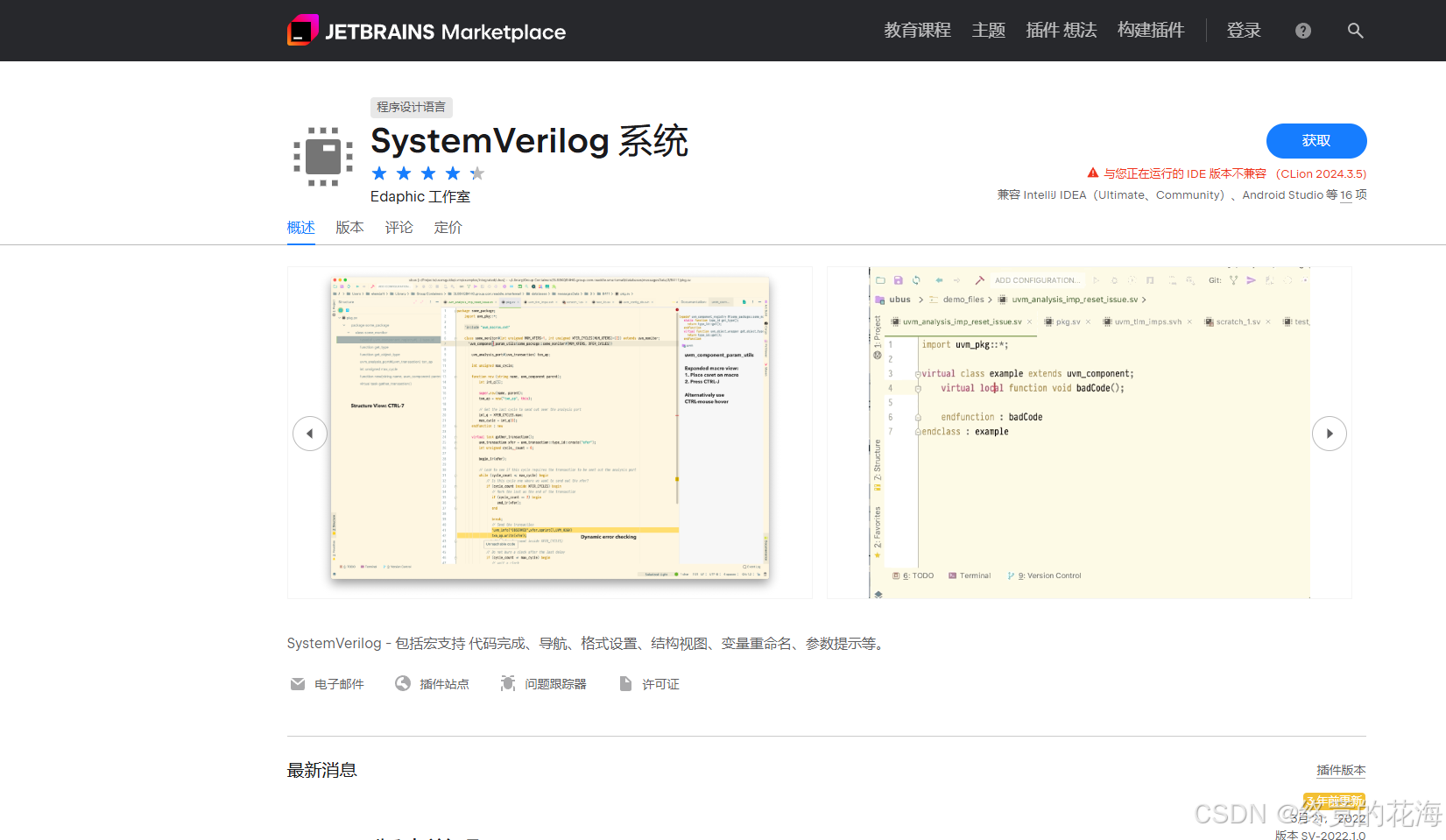

基于此,打算使用CLion试试。在官网上恰好看到了对应的插件,那么也就意味着此法可行。不过官方这个插件似乎还不支持所安装的CLion

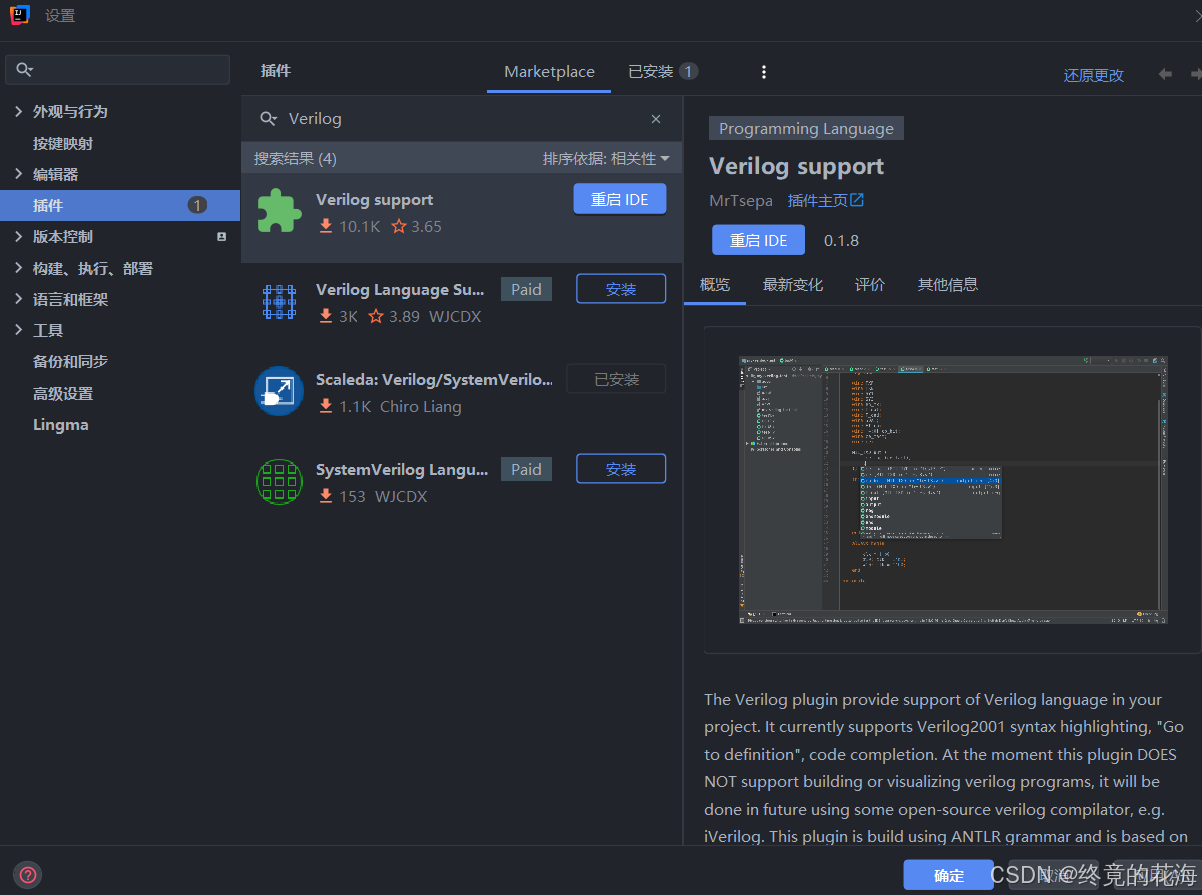

一、安装插件

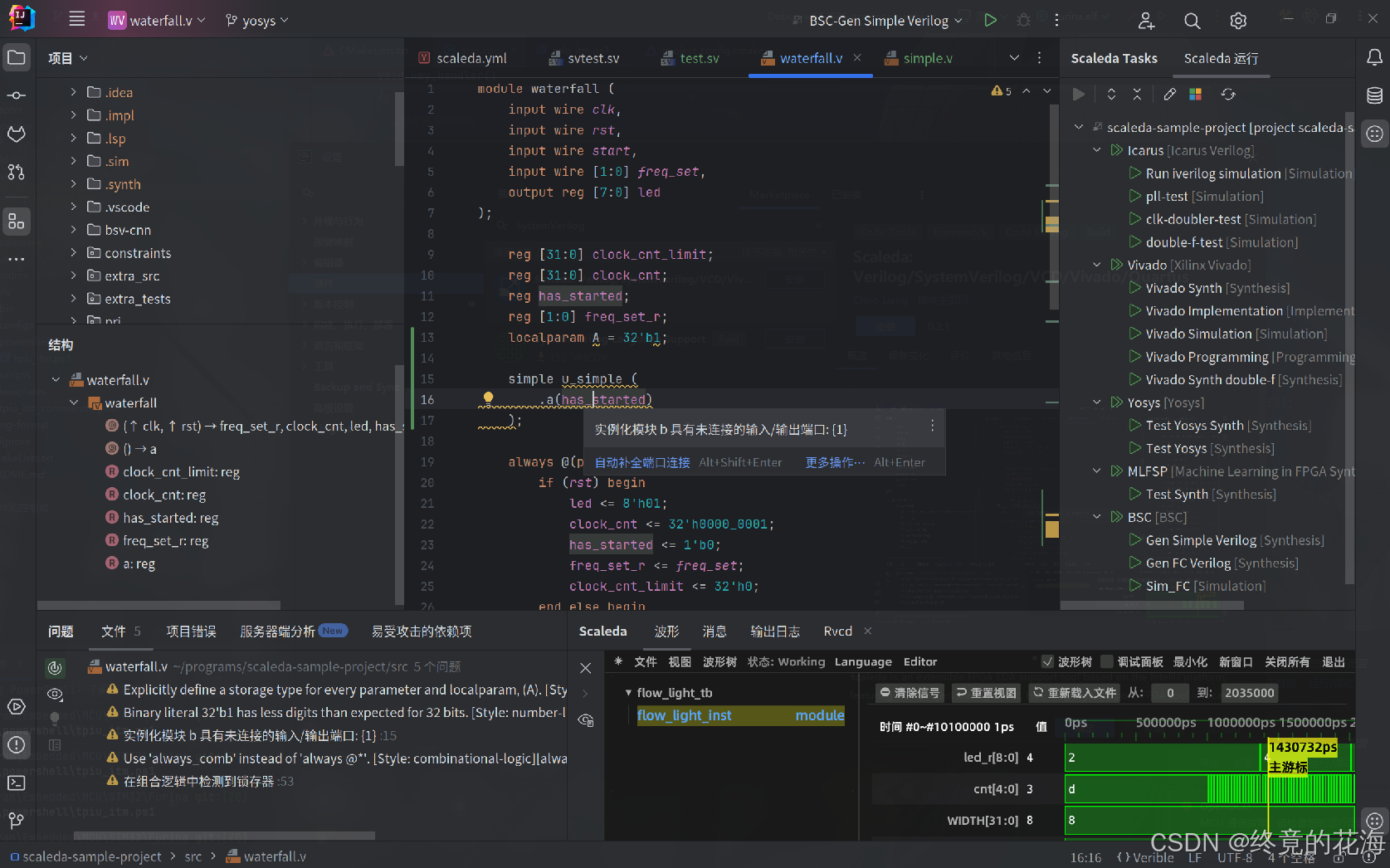

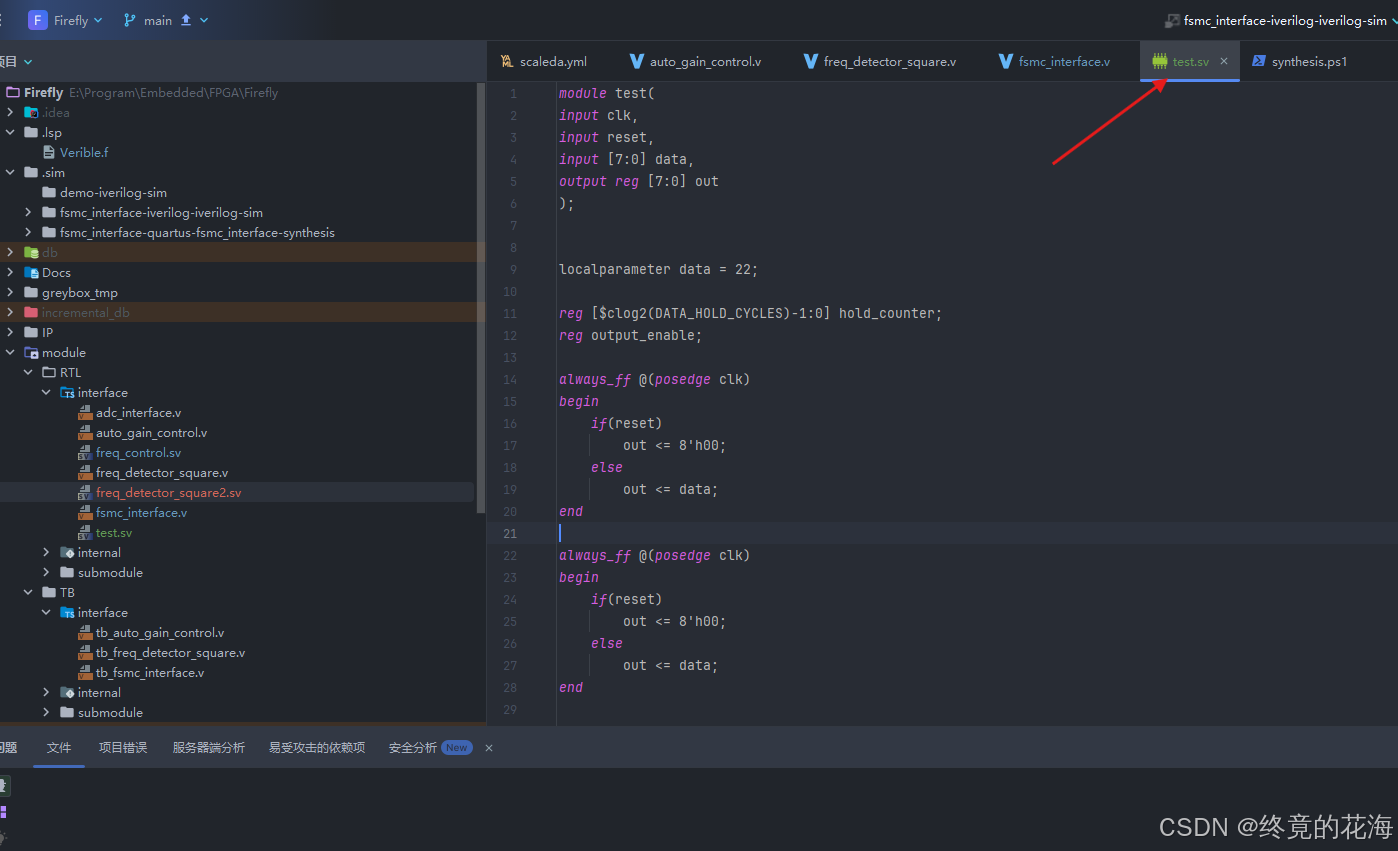

于是打算换成IntelliJ IDEA。下图中的第一个插件与VS Code下的差不多,有基本的代码补全功能,可以满足基本的Verilog开发。第三个插件有不少Verilog相关的代码检查等功能。

需要注意的是,后者与其他Verilog插件可能不兼容,所以需要作出取舍。此处使用后者,前者需要禁用,否则工程目录会一直处在正在加载

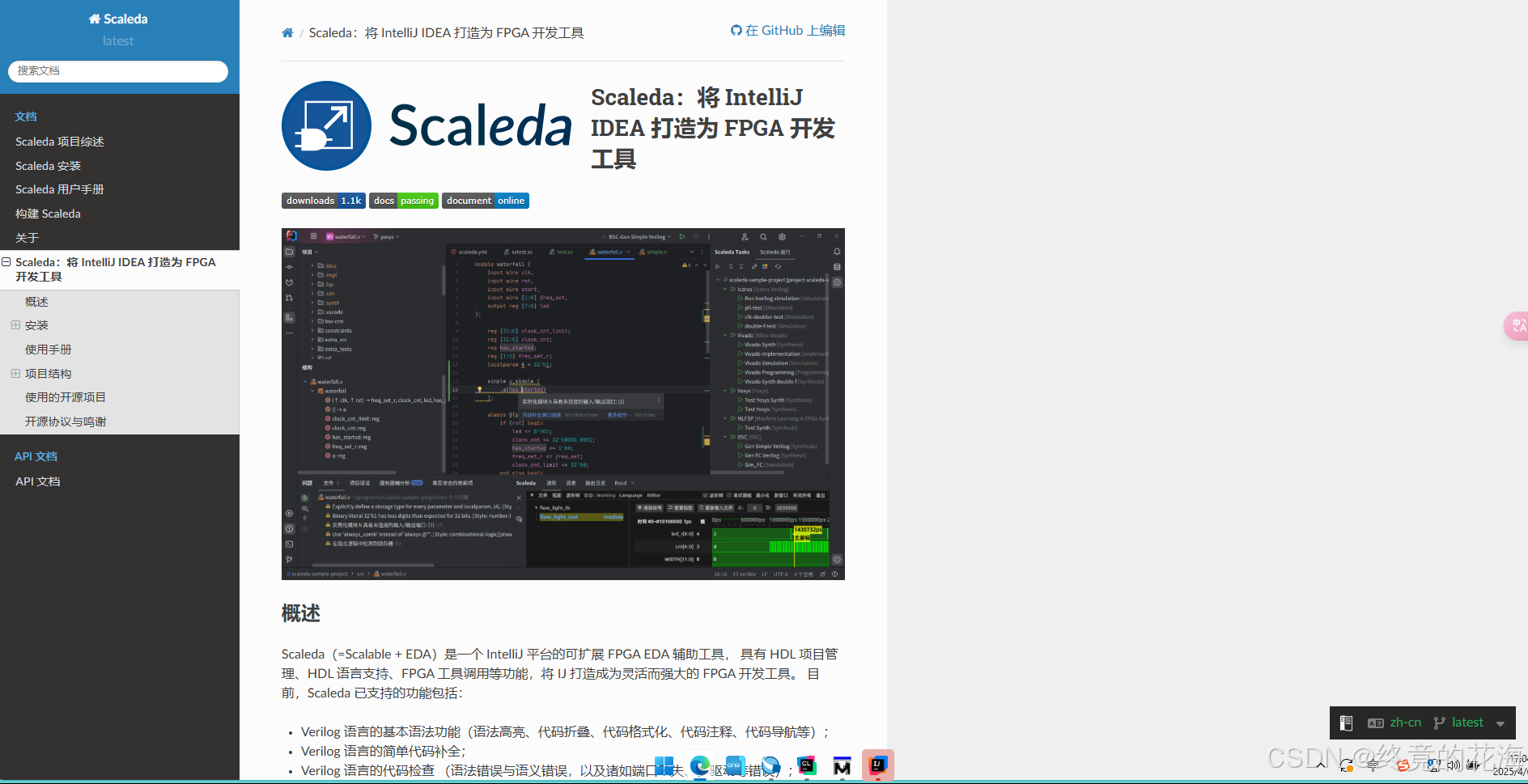

这个牛掰的插件,同时也是开源项目。

教程文档:Scaleda:将 IntelliJ IDEA 打造为 FPGA 开发工具 — Scaleda v0.2.1 文档

手册:快速开始 — Scaleda v0.2.1 文档

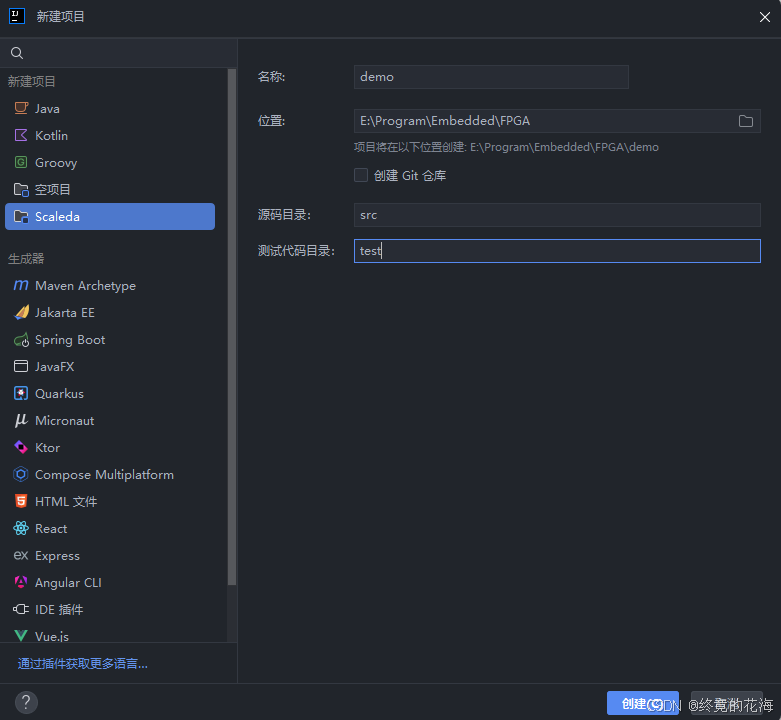

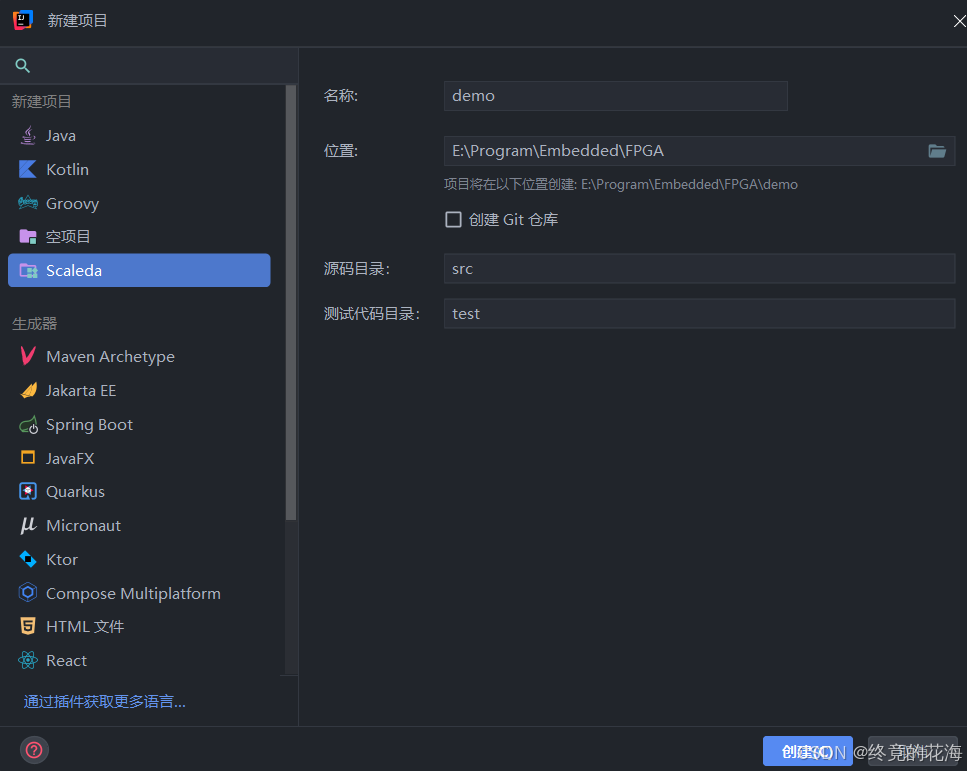

二、创建新项目

1,创建工程

新建项目,指定好路径,路径不能有中文。下图这个Scaleda图标表明插件不兼容

图标实际应为

创建后会自动生成下面文件

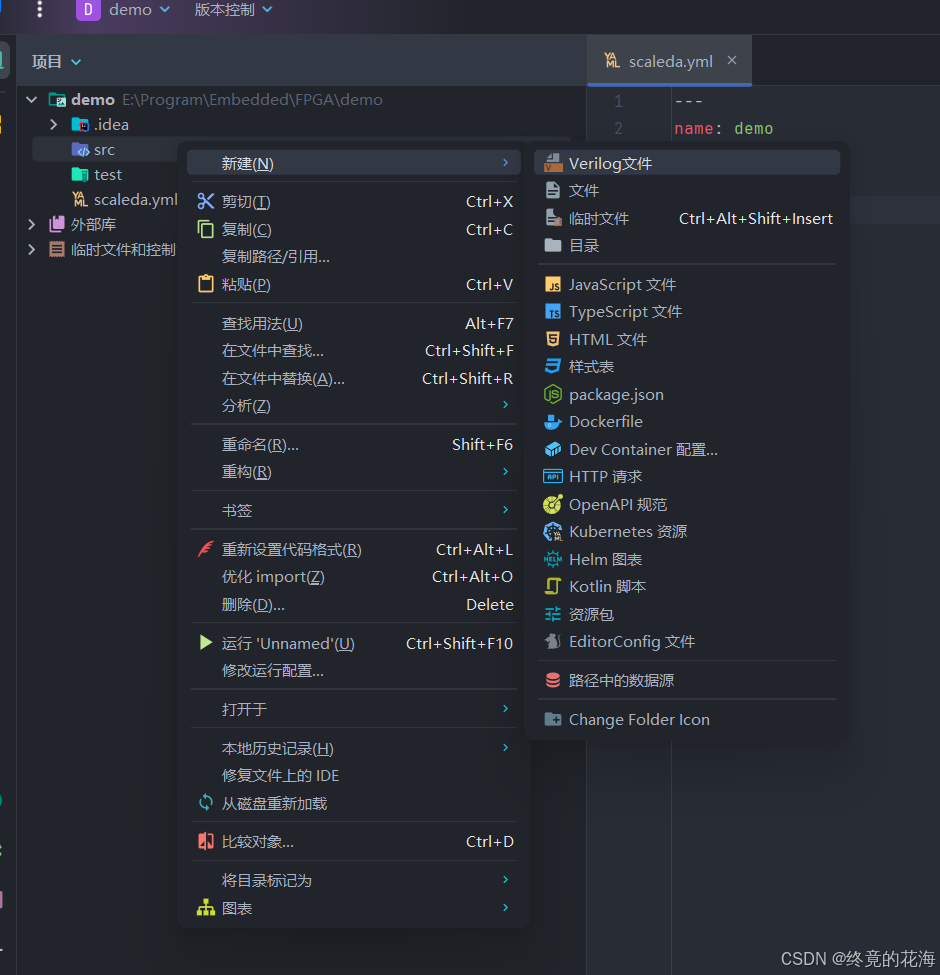

2,新建文件

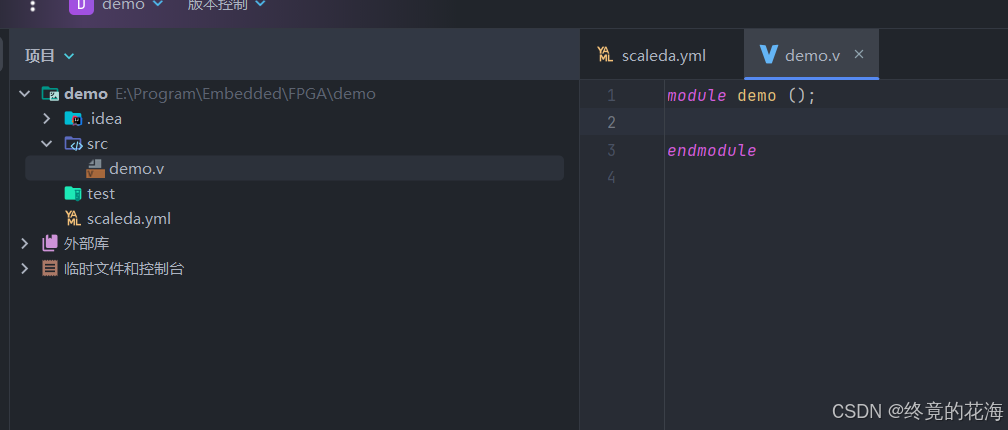

①新建Verilog文件

新建后,会自动生成对应框架

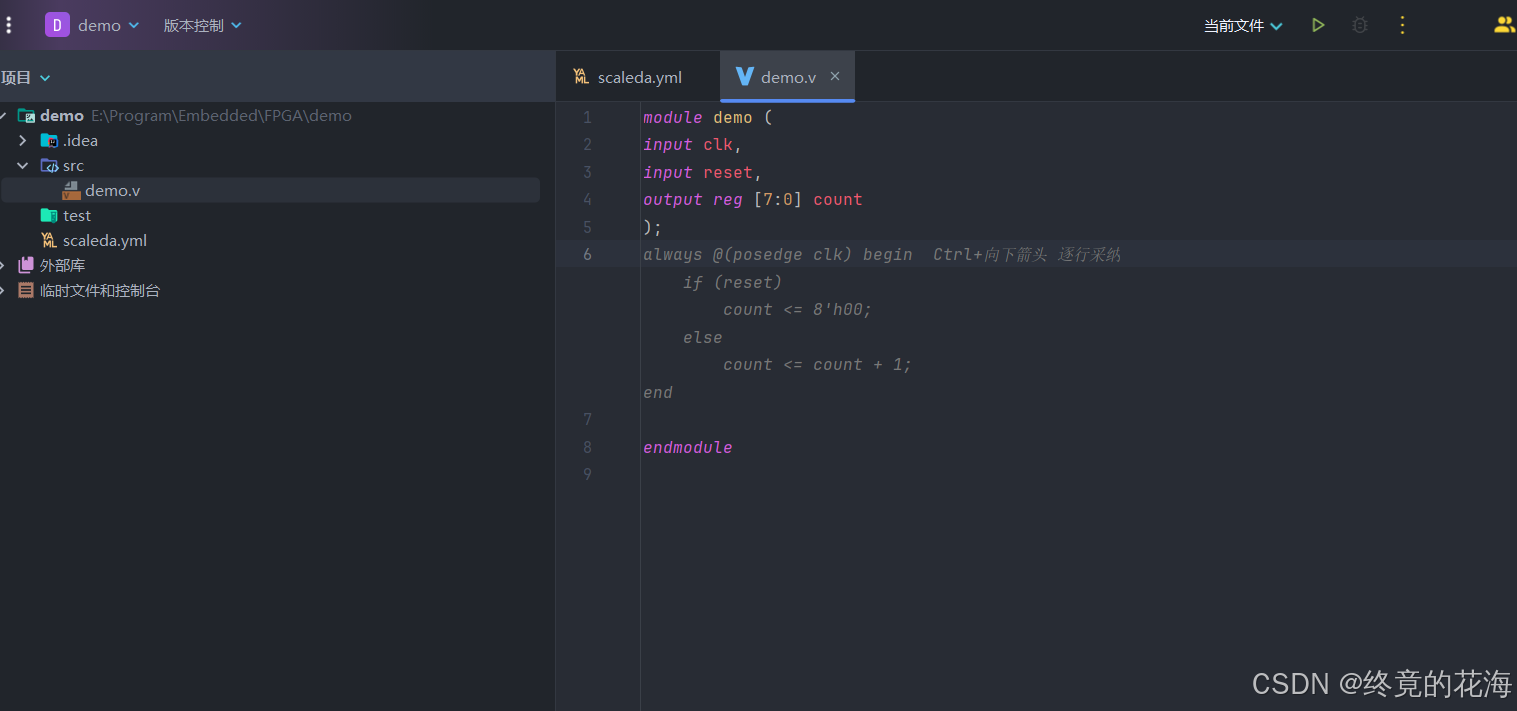

先写一个简单的计数器模块,在强大的代码补全和代码提示下,很轻松地完成了

module demo ( input clk, input reset, output reg [7:0] count ); always @(posedge clk) beginif (reset)count <= 8'h00;elsecount <= count + 1; endendmodule②新建Testbench文件

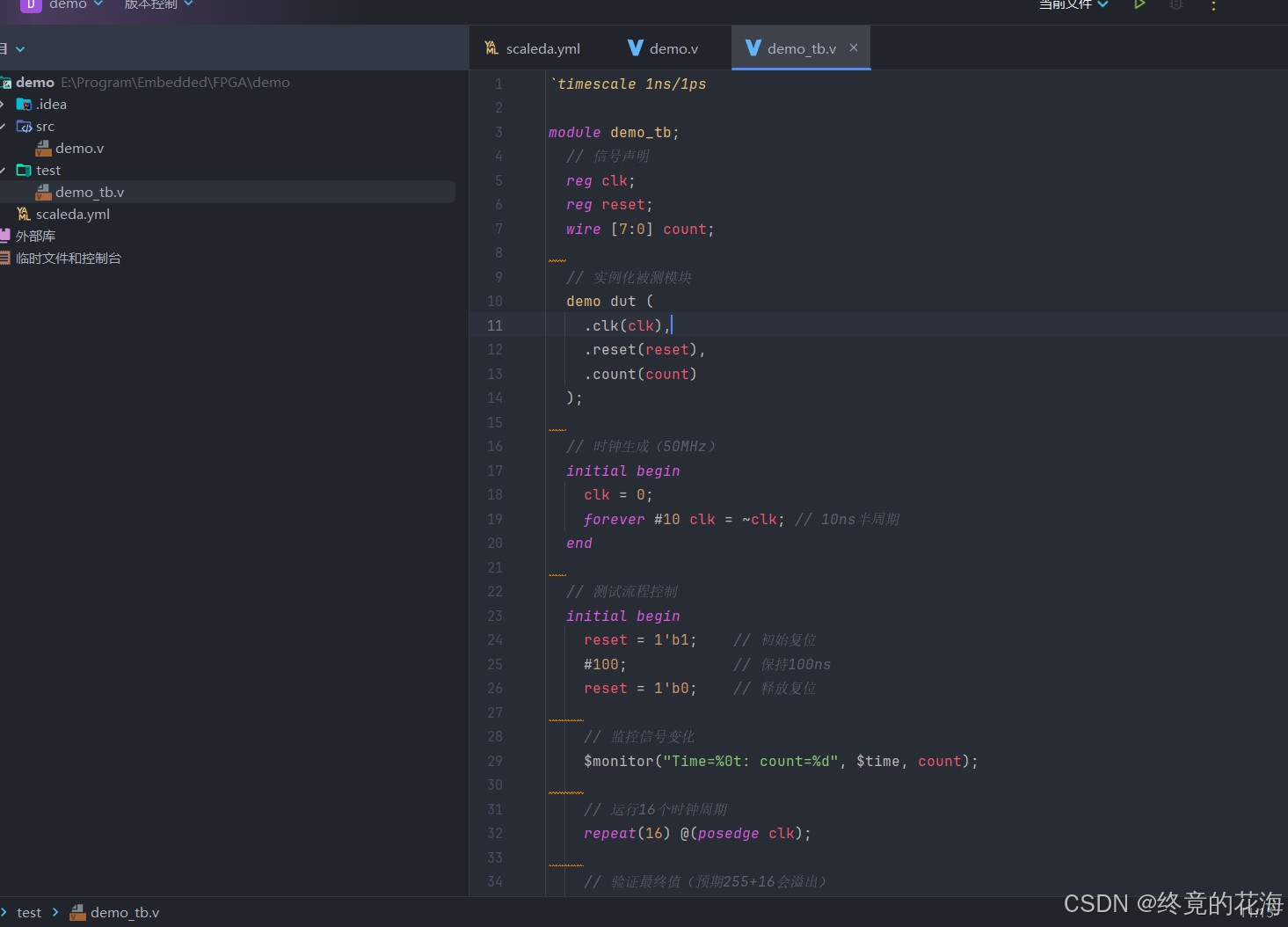

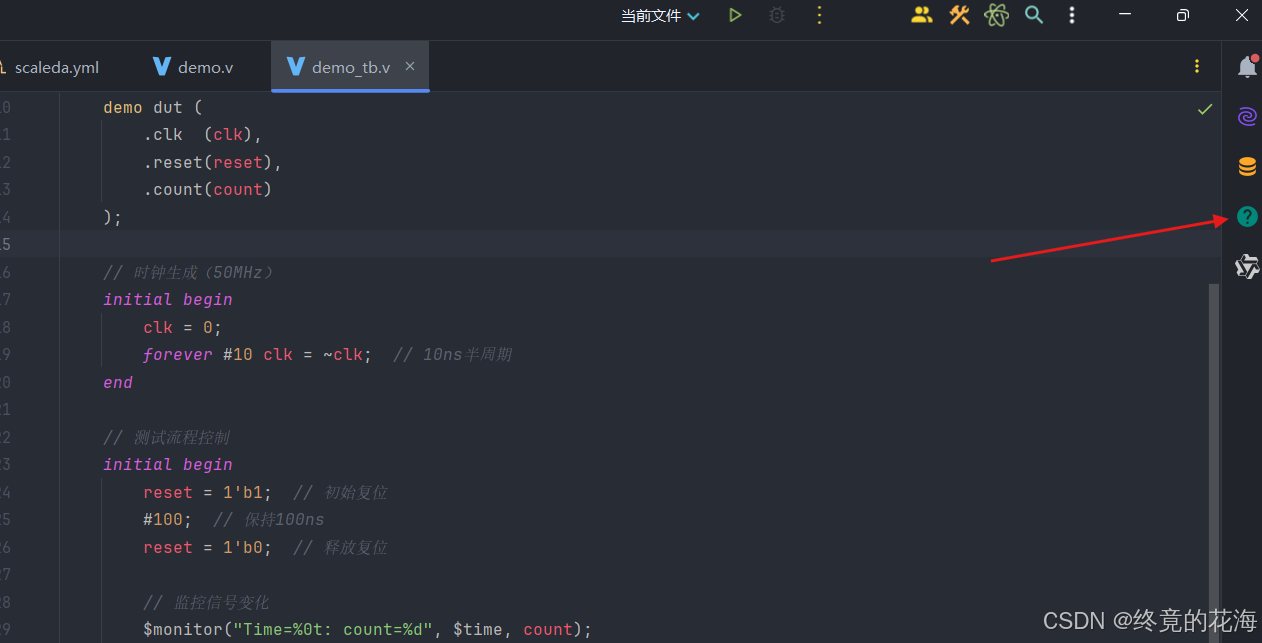

先简单写一个测试激励文件

`timescale 1ns / 1psmodule demo_tb;// 信号声明reg clk;reg reset;wire [7:0] count;// 实例化被测模块demo dut (.clk (clk),.reset(reset),.count(count));// 时钟生成(50MHz)initial beginclk = 0;forever #10 clk = ~clk; // 10ns半周期end// 测试流程控制initial beginreset = 1'b1; // 初始复位#100; // 保持100nsreset = 1'b0; // 释放复位// 监控信号变化$monitor("Time=%0t: count=%d", $time, count);// 运行16个时钟周期repeat (16) @(posedge clk);// 验证最终值(预期255+16会溢出) // if (count !== 8'd15) begin // $error("Final count mismatch! Expected 15, got %d", count); // end$finish;end// 这段语句会自动生成,所以不用加 // // VCD波形记录 // initial begin // $dumpfile("demo_tb_waveform.vcd"); // $dumpvars; // 记录测试台顶层信号 // end endmodule③格式化文件

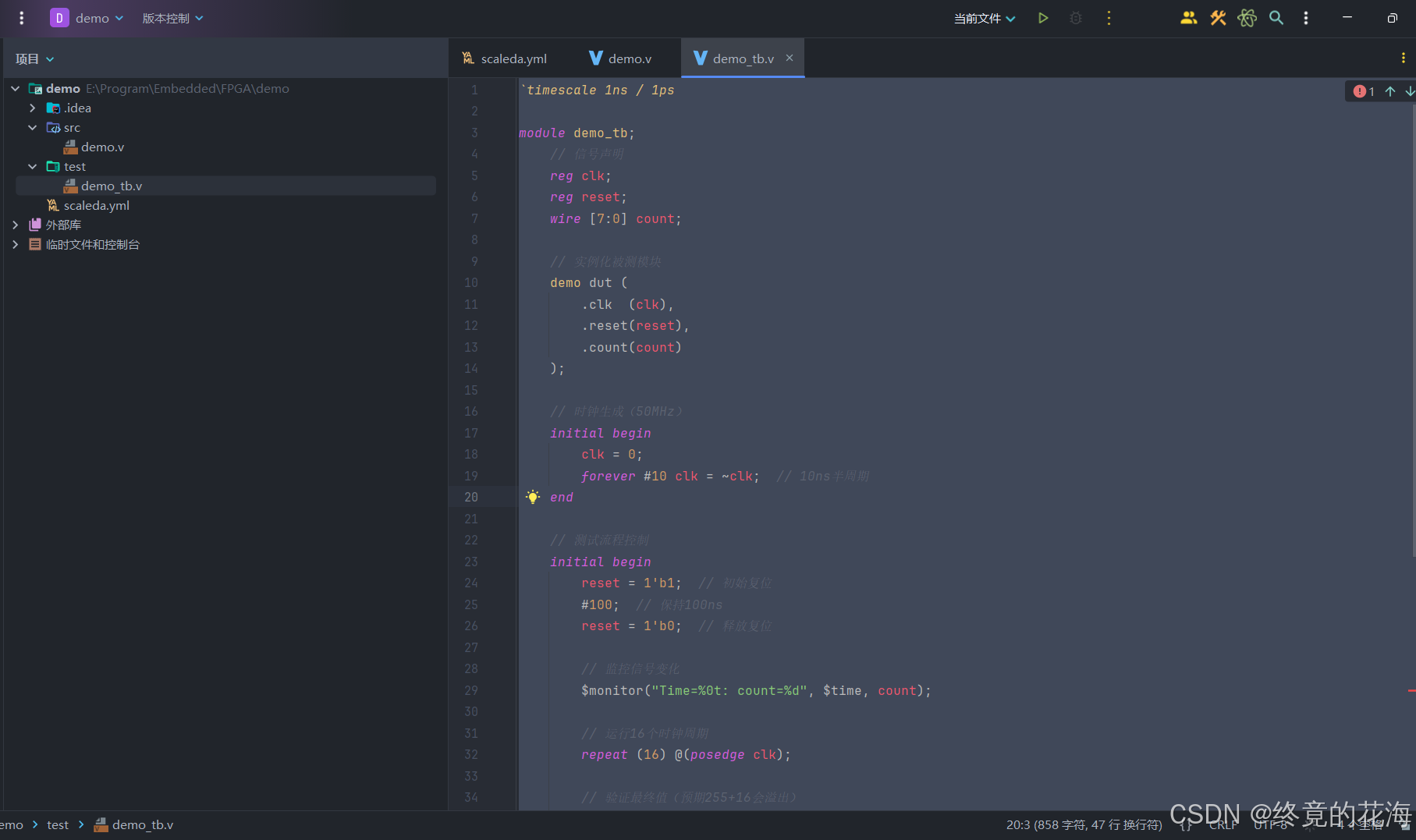

从上图可以看出,有很多警告表示应用Tab代替空格。

可以先按Ctrl + A全选,然后再按Ctrl + Alt + L 格式化代码

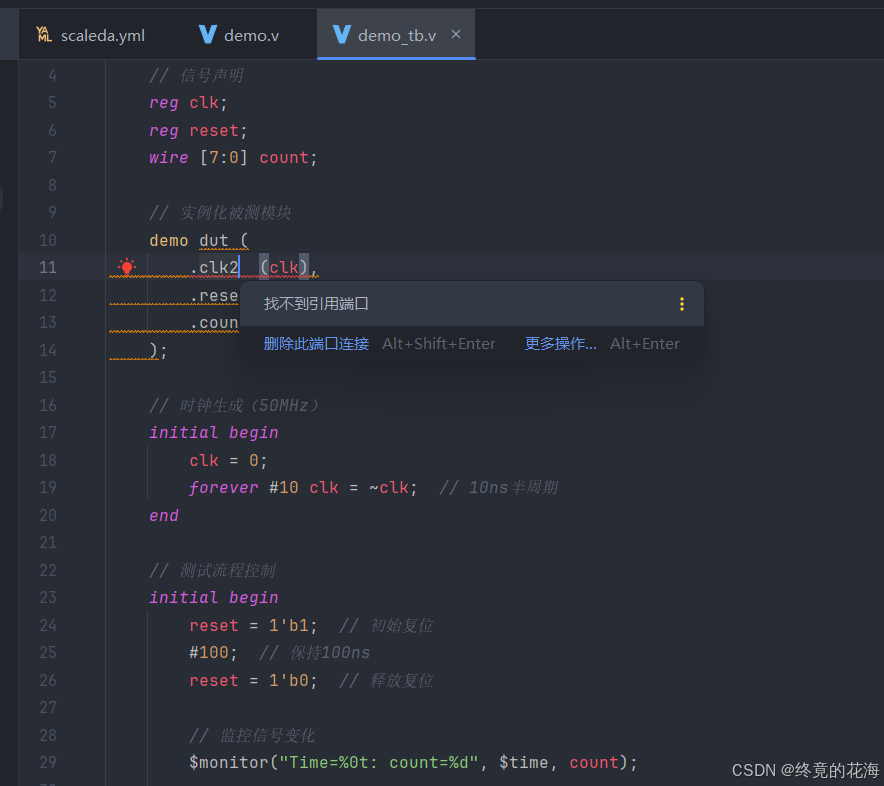

④代码检查

代码出现问题,不仅会有报错提示,还有对应的解决措施,成功地把编写代码的难度降低一大截

3,基本功能

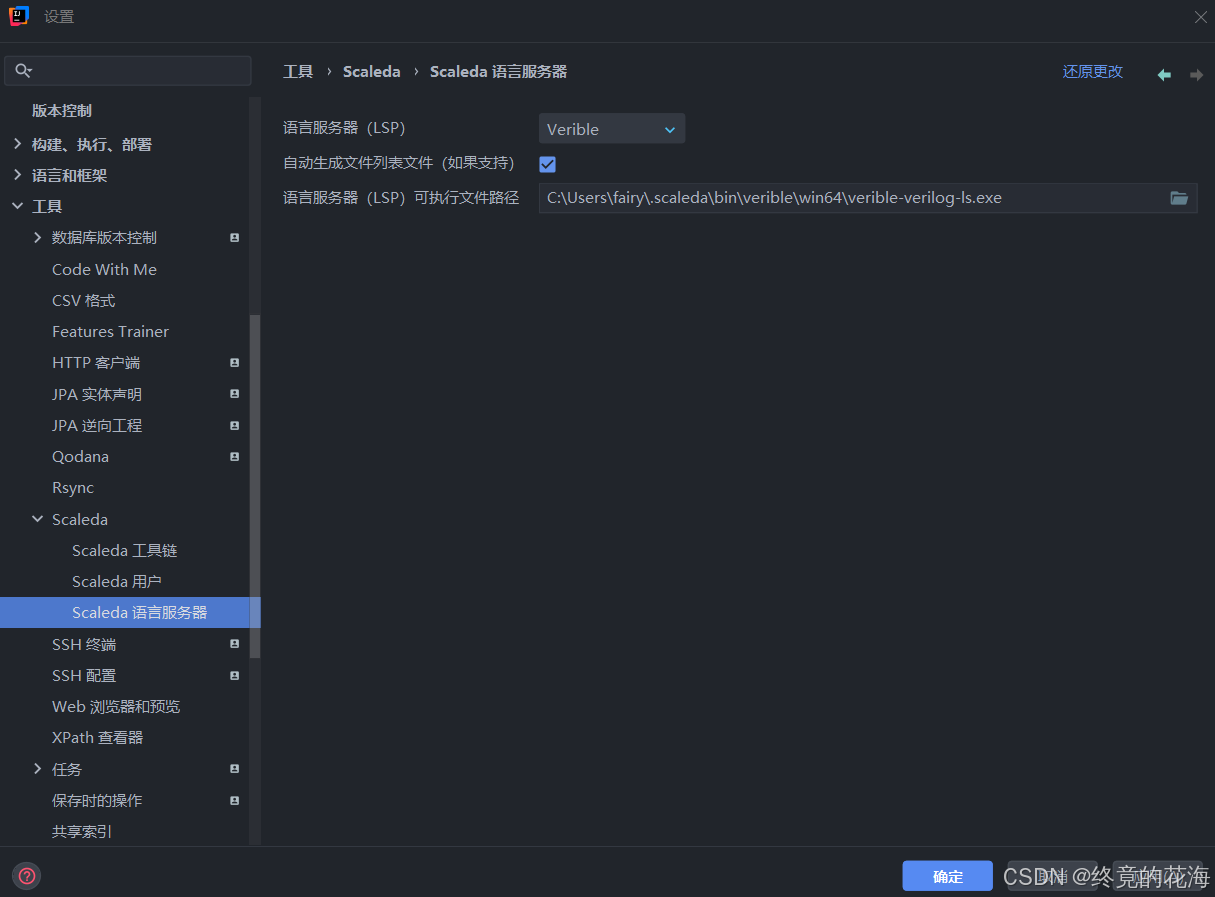

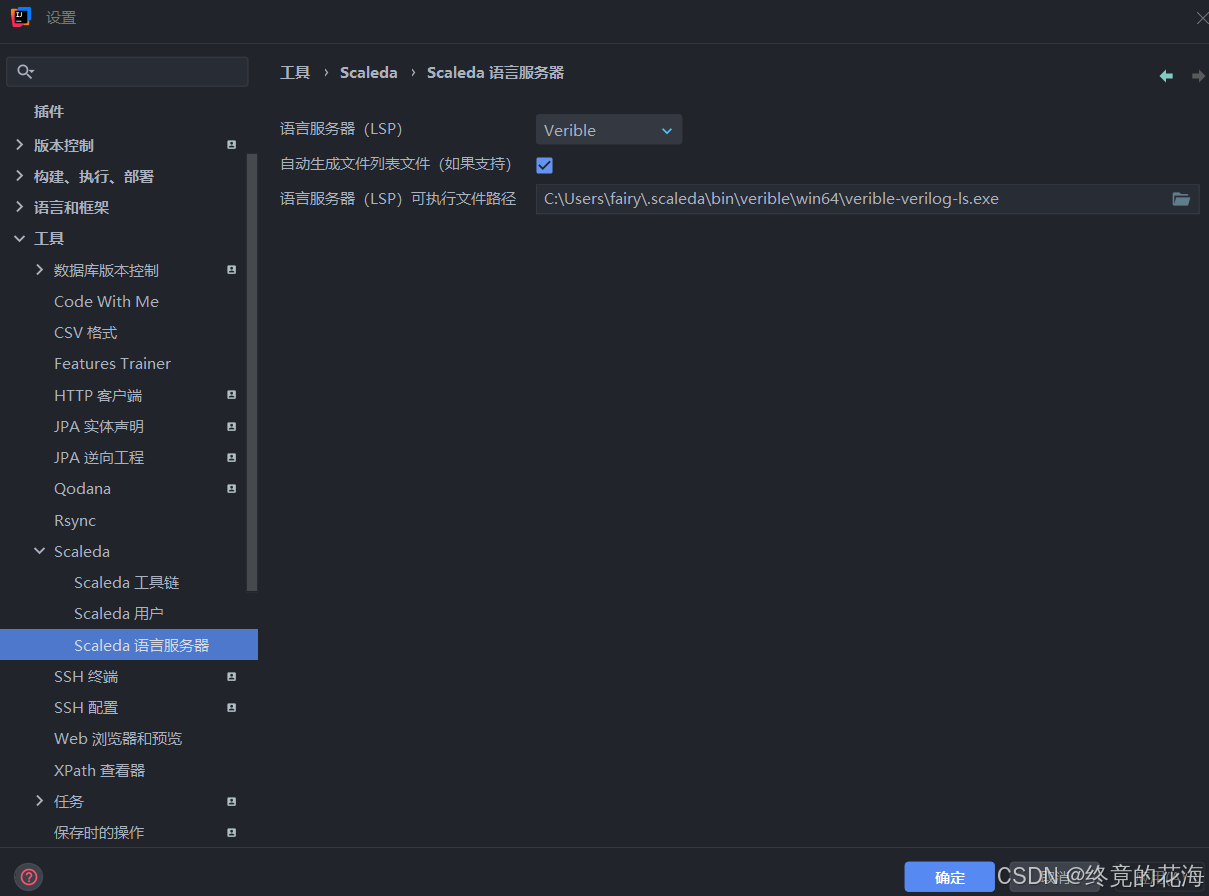

①语言服务器

在设置中可以找到该插件的相关配置,首先是如图的语言服务器(LSP),提供代码检查等功能

Verible是检测Verilog的,svls则是检测System Verilog

手册中亦有记载

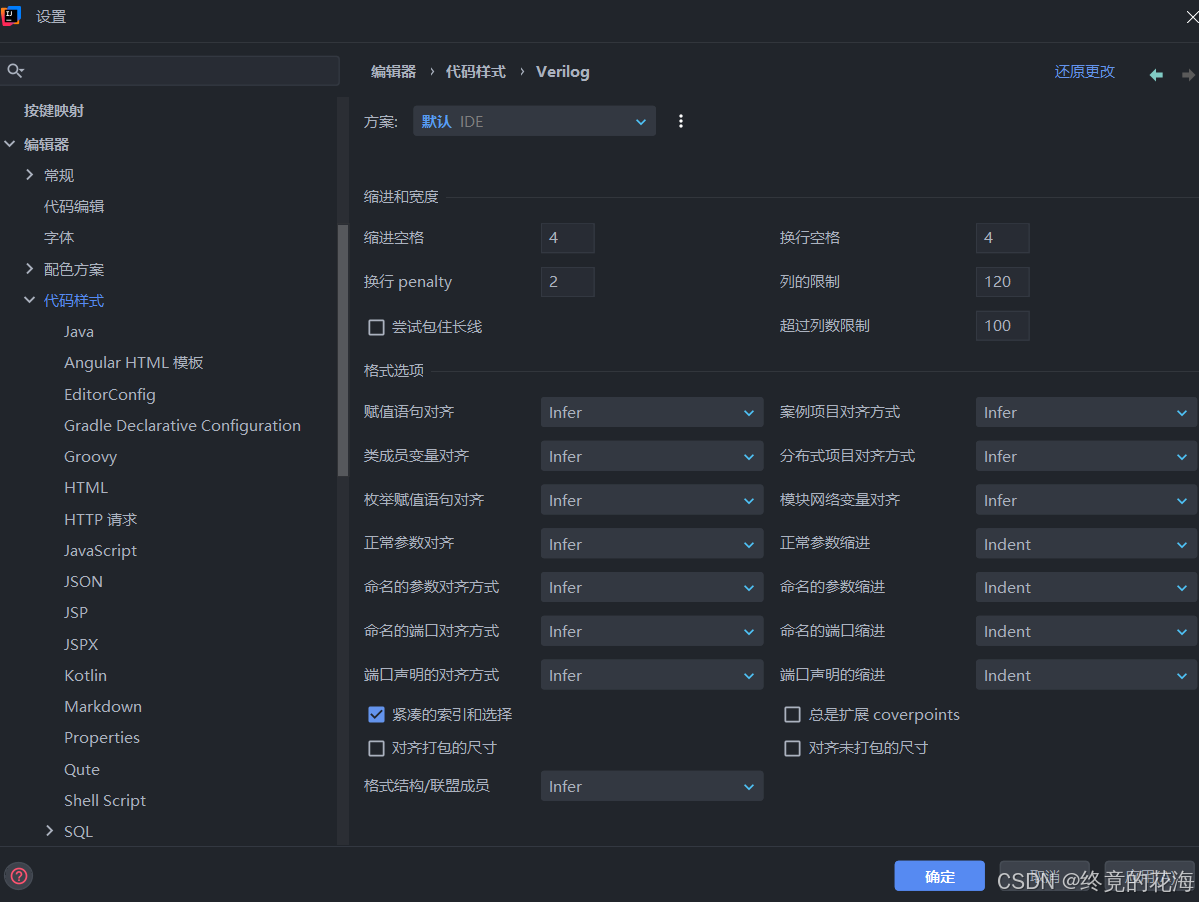

②代码样式

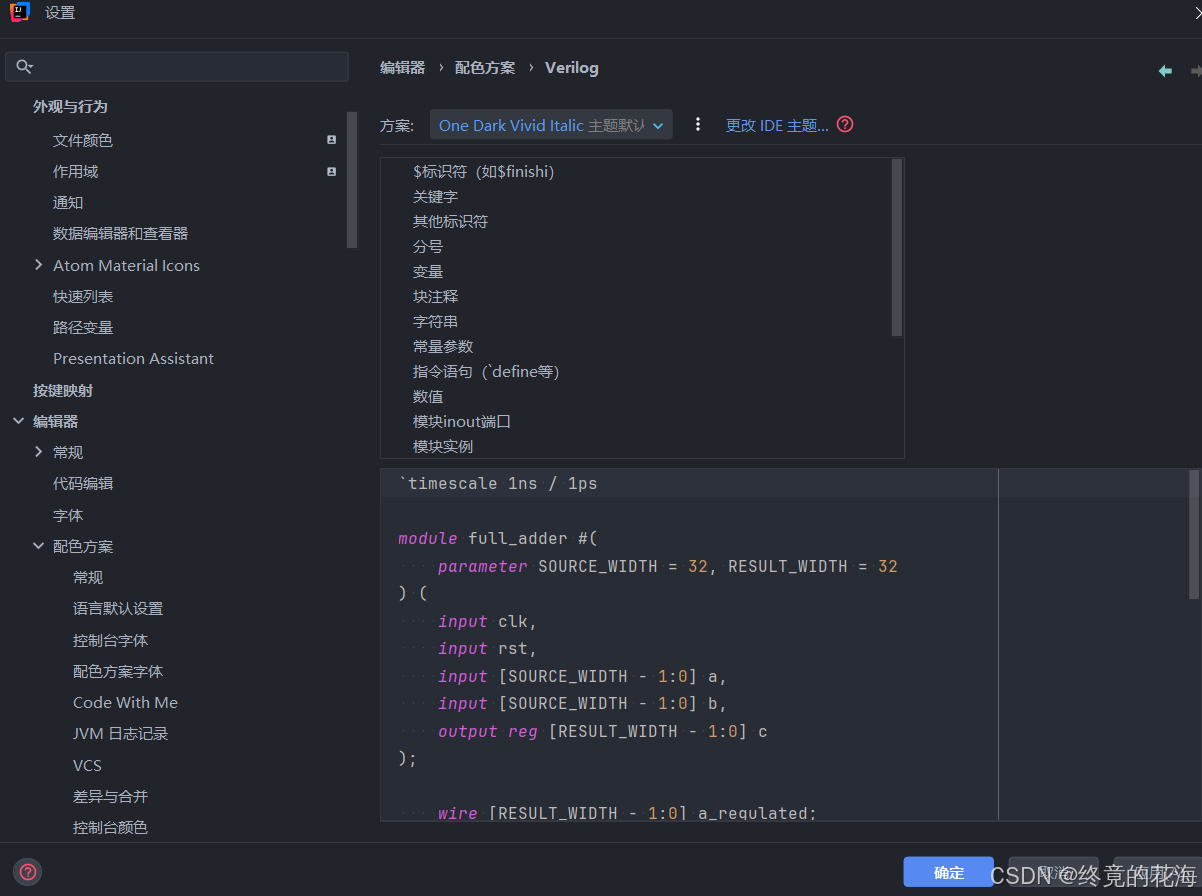

③配色方案

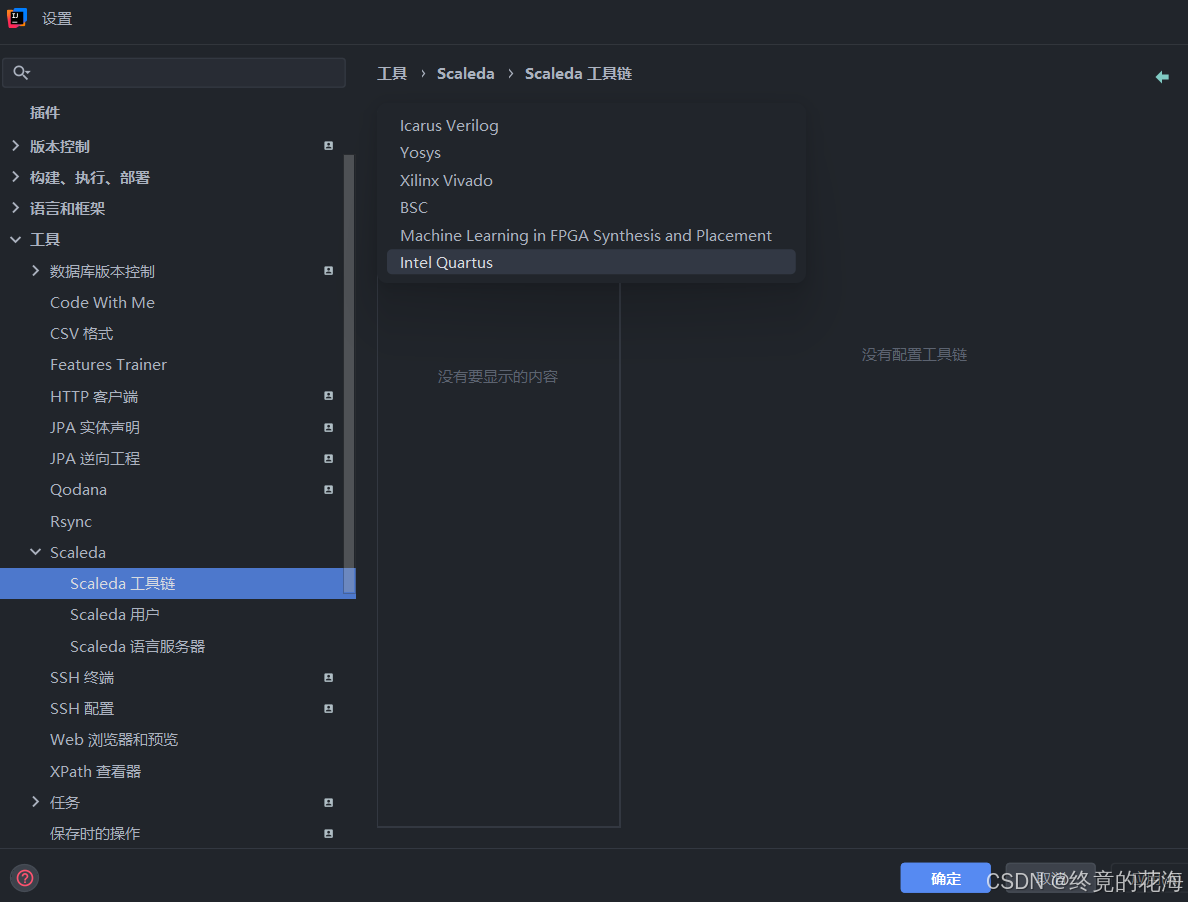

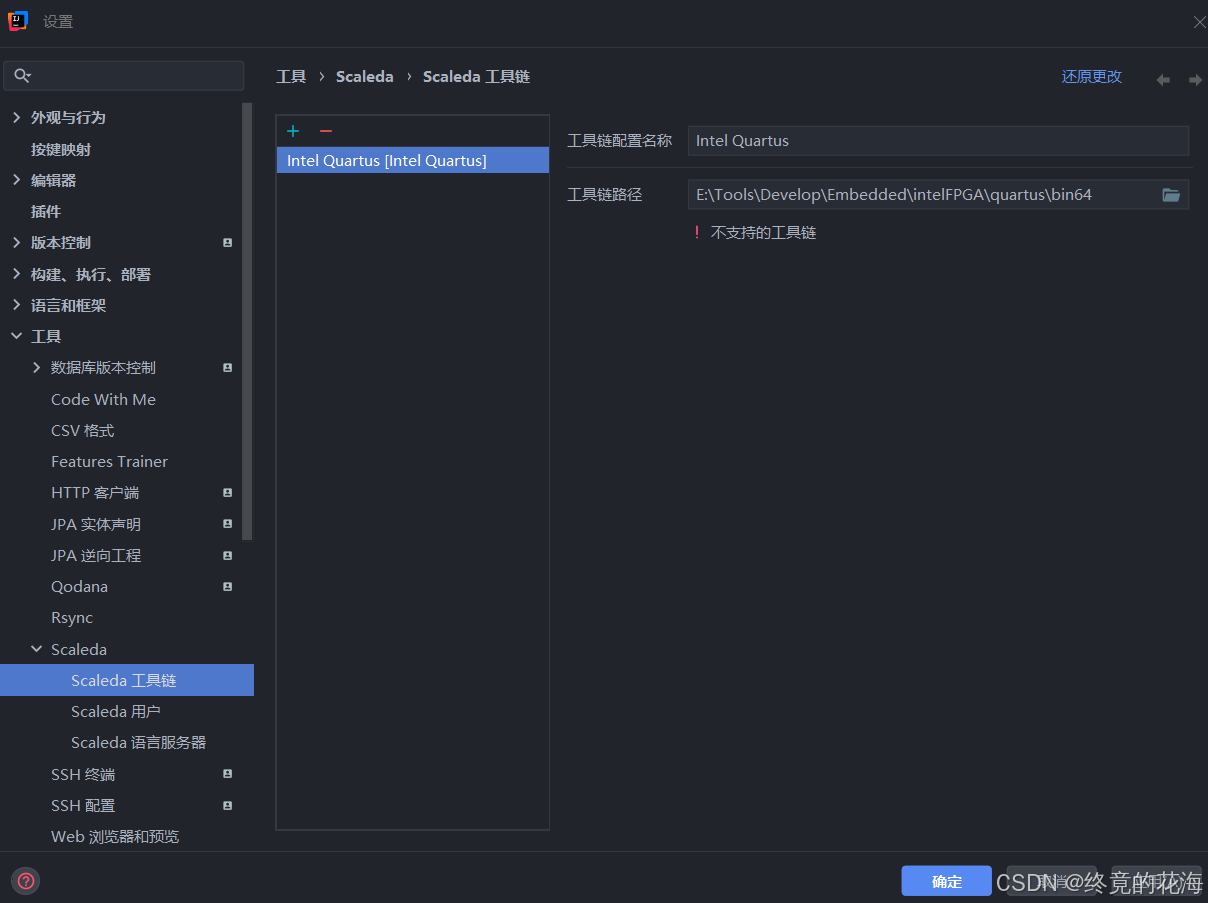

4,添加工具链

①Intel Quartus

由于本人使用的是Quartus,所以添加的是Quartus的工具链,Vivado等在手册中有相关配置教程

点击添加,会有多个工具链模板,选择最后一个Intel Quartus

在Quartus的安装路径中找到bin64这个路径即可

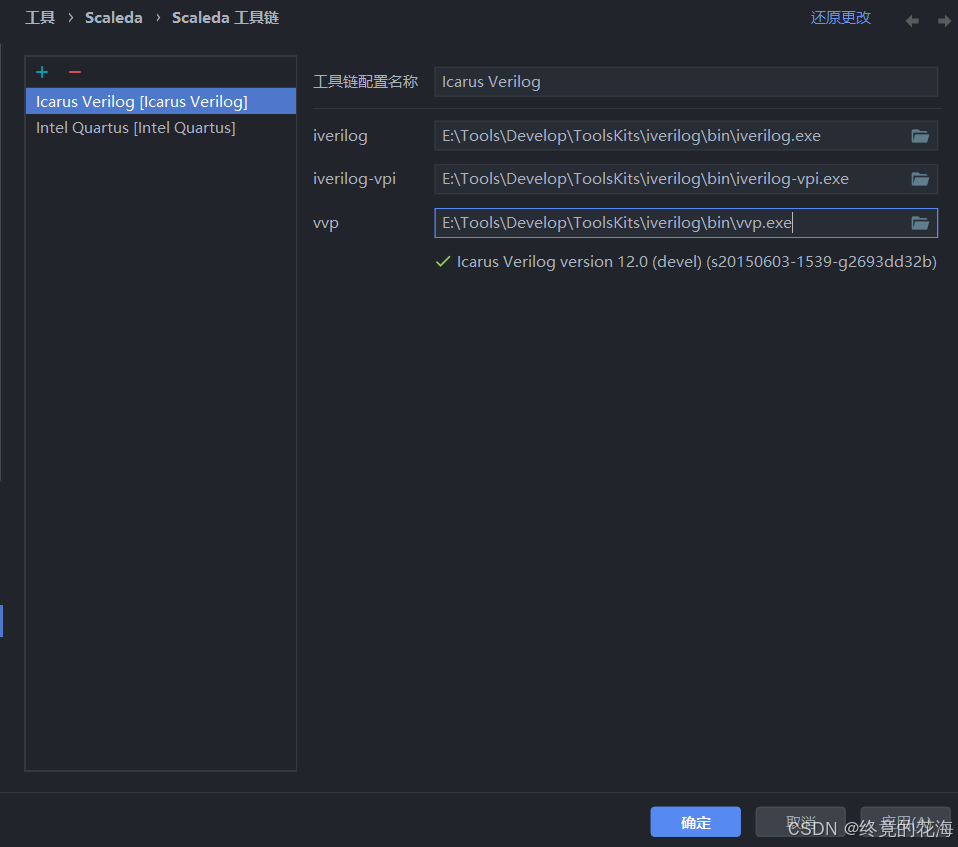

②Icarus Verilog

Intel Quartus是FPGA的综合和实现工具,而Icarus Verilog是开源仿真器,主要用于验证HDL代码

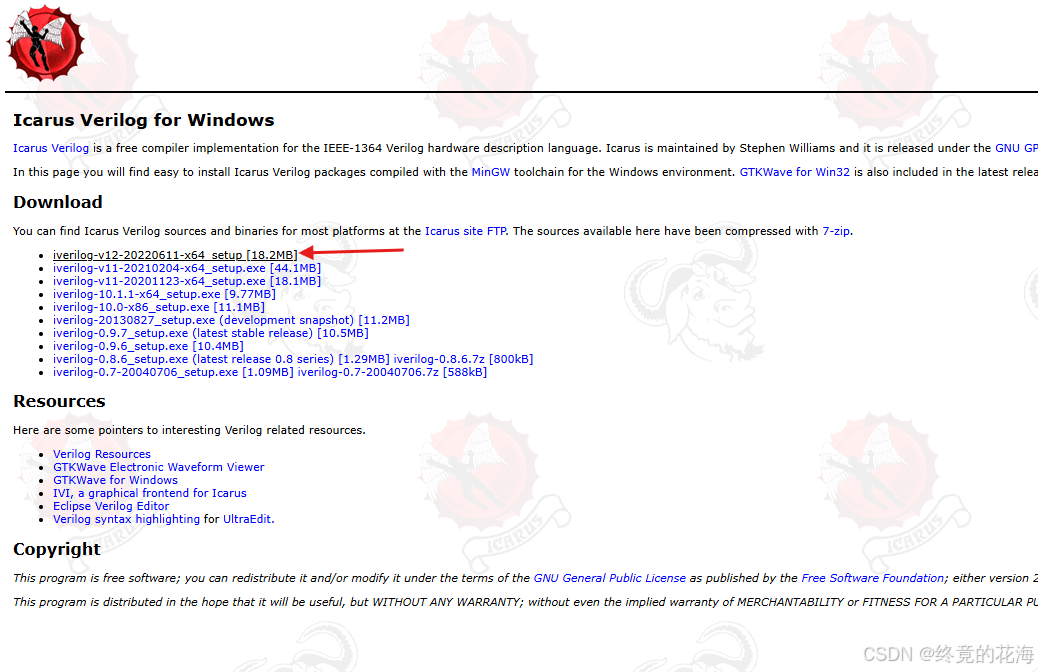

下载

进入网址Icarus Verilog for Windows,然后选择对应版本下载,比如最新版

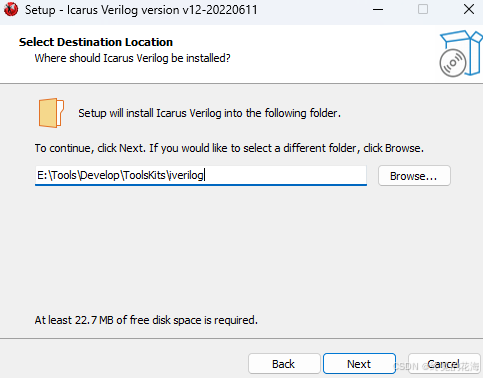

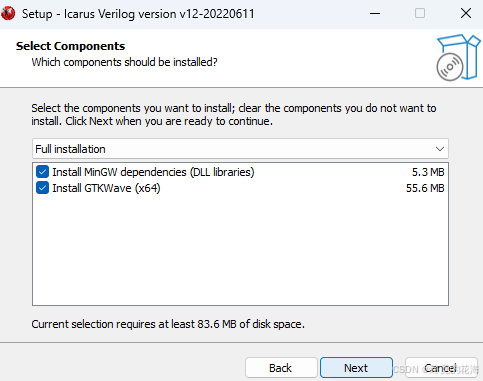

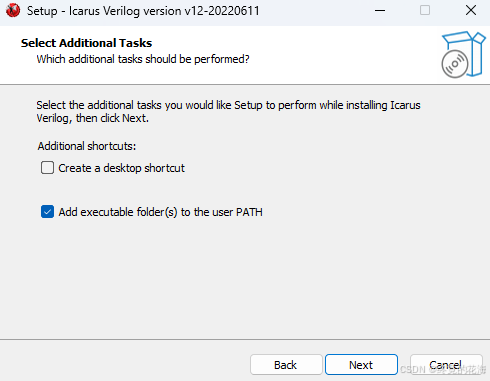

安装

选择合适的目录即可

可以选择添加环境变量,环境变量若想生效,需要重启(此时可以不重启)

安装完成后就可以添加该工具链了,由于已经包含了所需的三个程序,故路径非常简单。但要注意,此时需要指向程序,而非目录

5,添加仿真配置

①添加目标平台

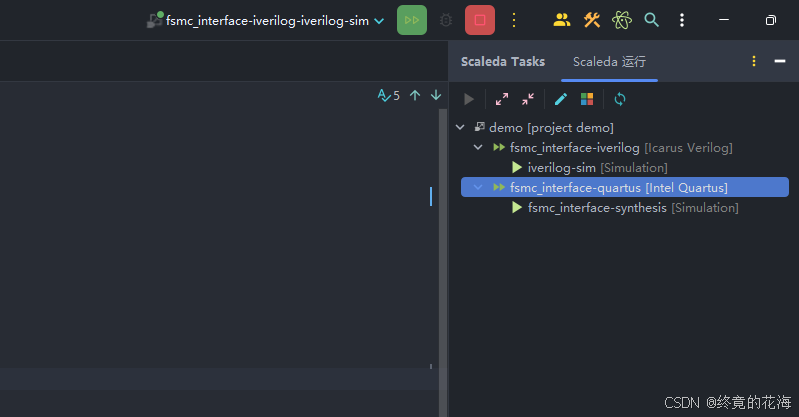

点击右上角的任务视图

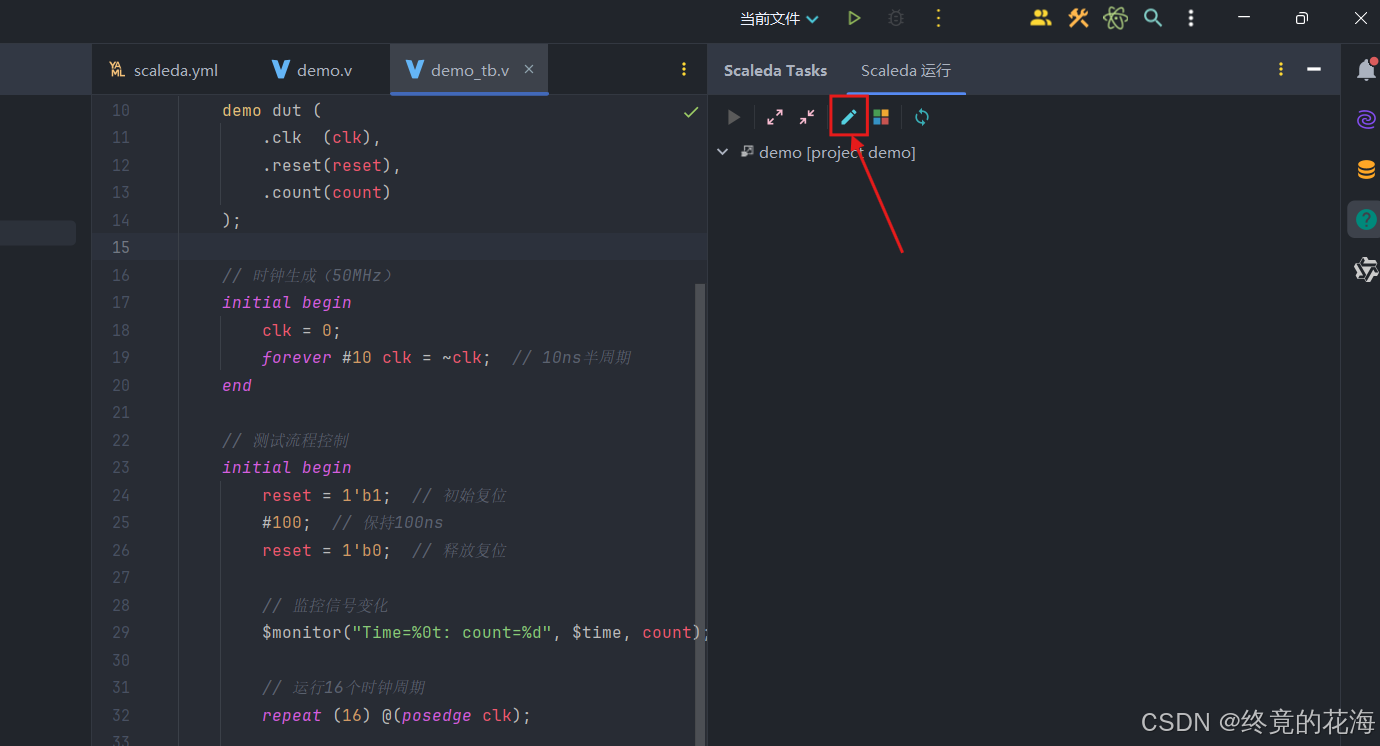

再点击编辑任务

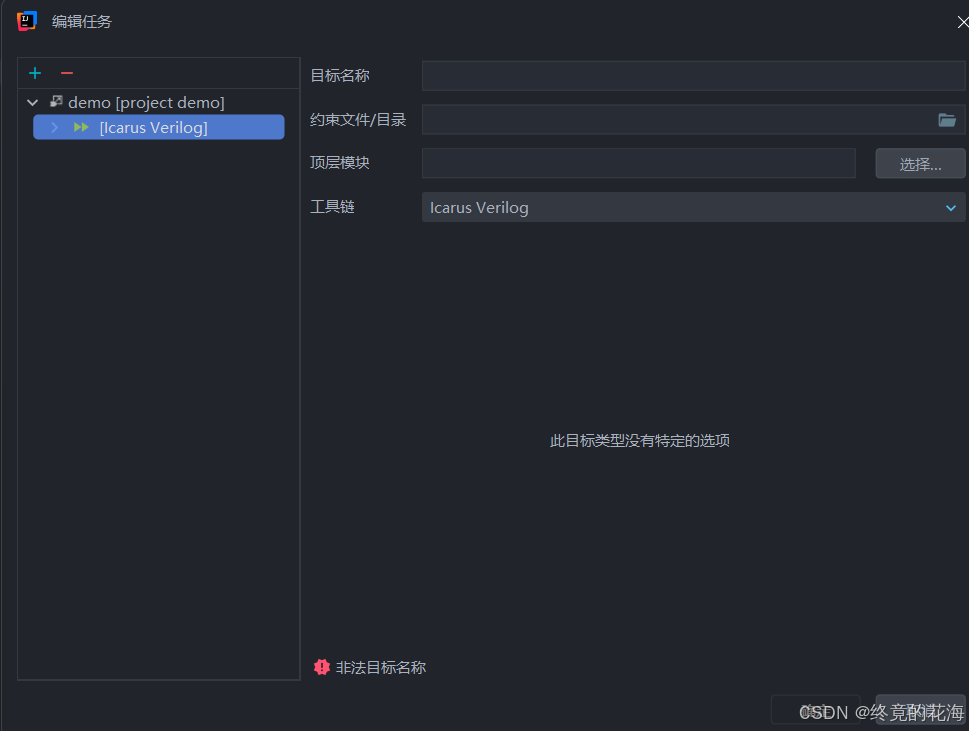

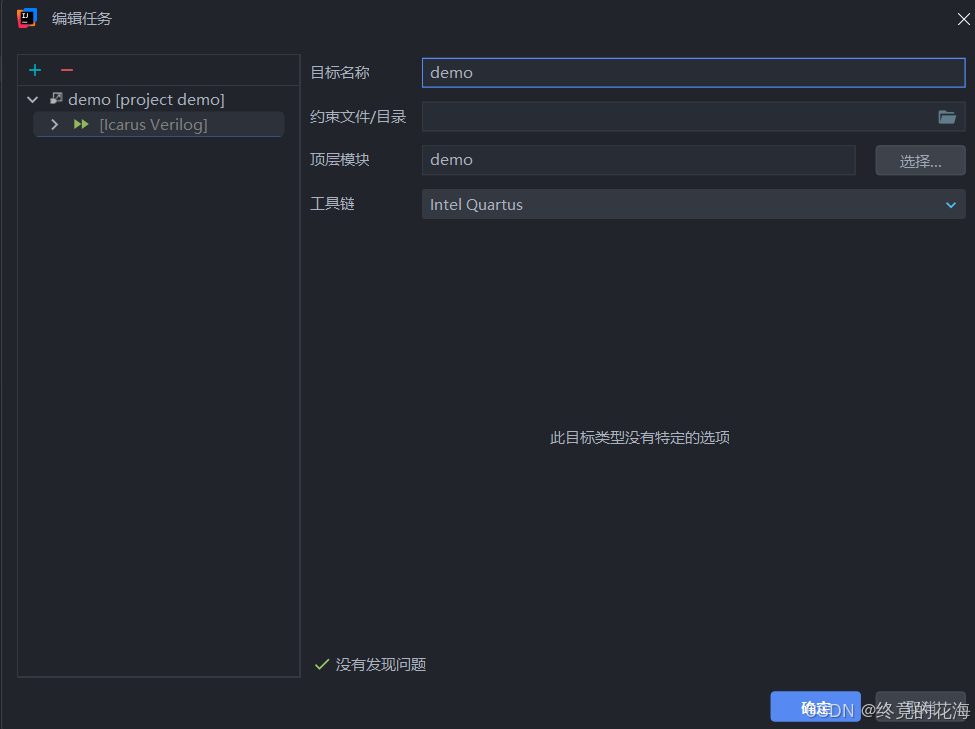

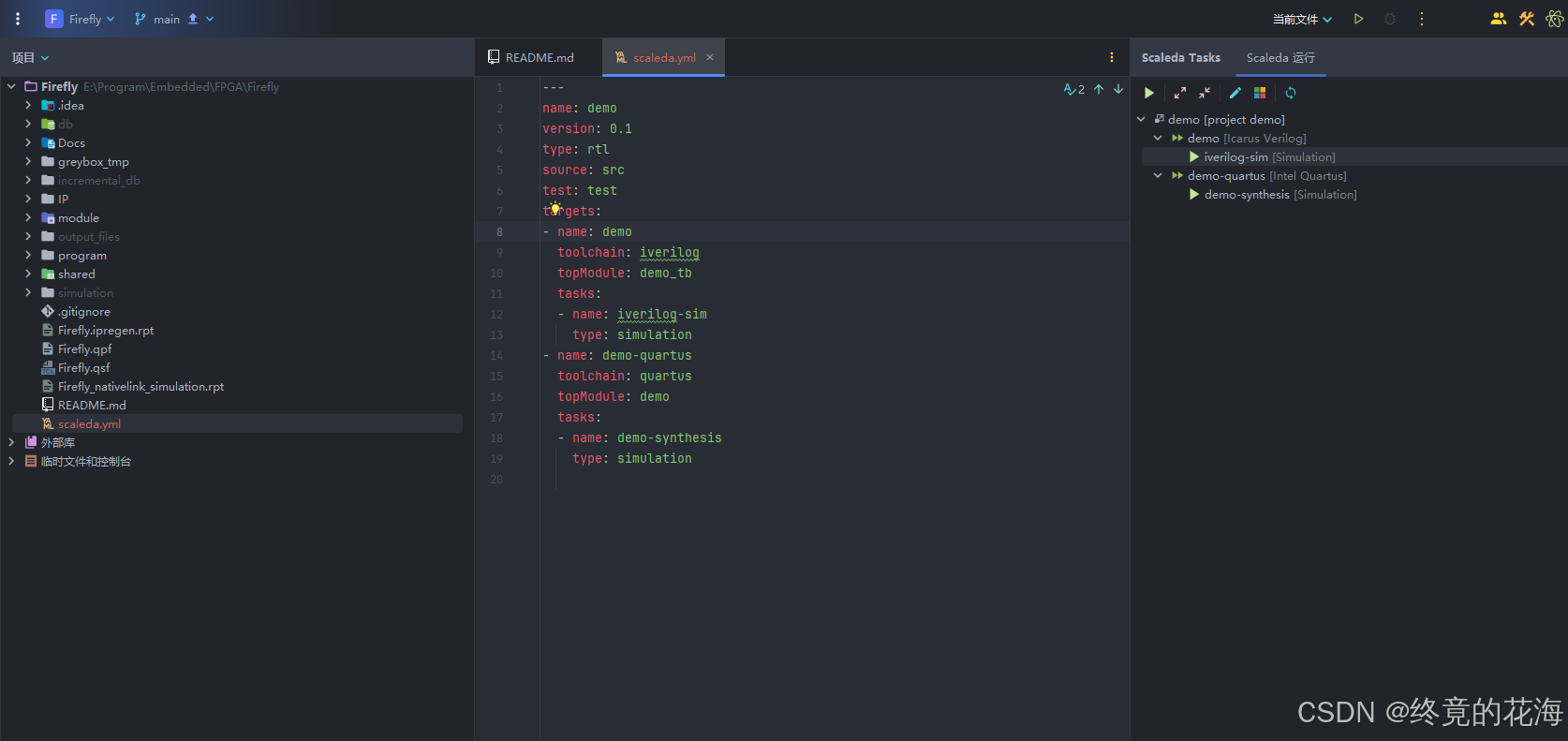

然后点击“+”,会出现一个目标平台,选择对应的目标名称、工具链和顶层模块

顶层模块,这里应添demo,而非demo_tb。约束文件暂时不管

②添加仿真任务

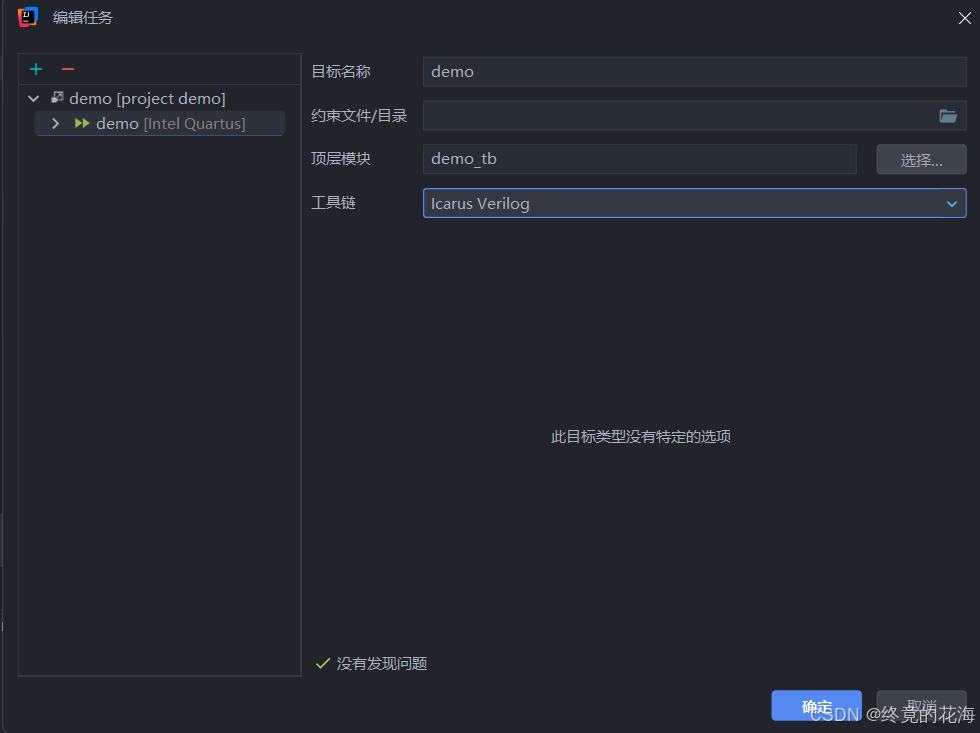

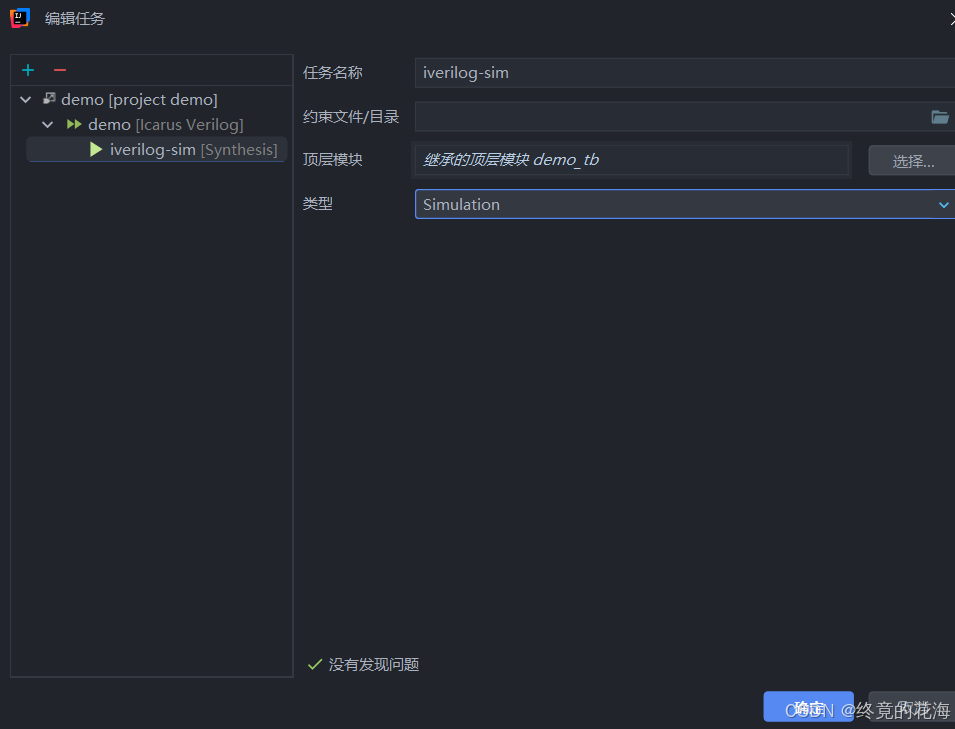

点击目标平台后,再点击这个目标平台,然后点击“+”来添加仿真项目。注意!是仿真任务,所以使用的工具链是Icarus Verilog这个开源工具链

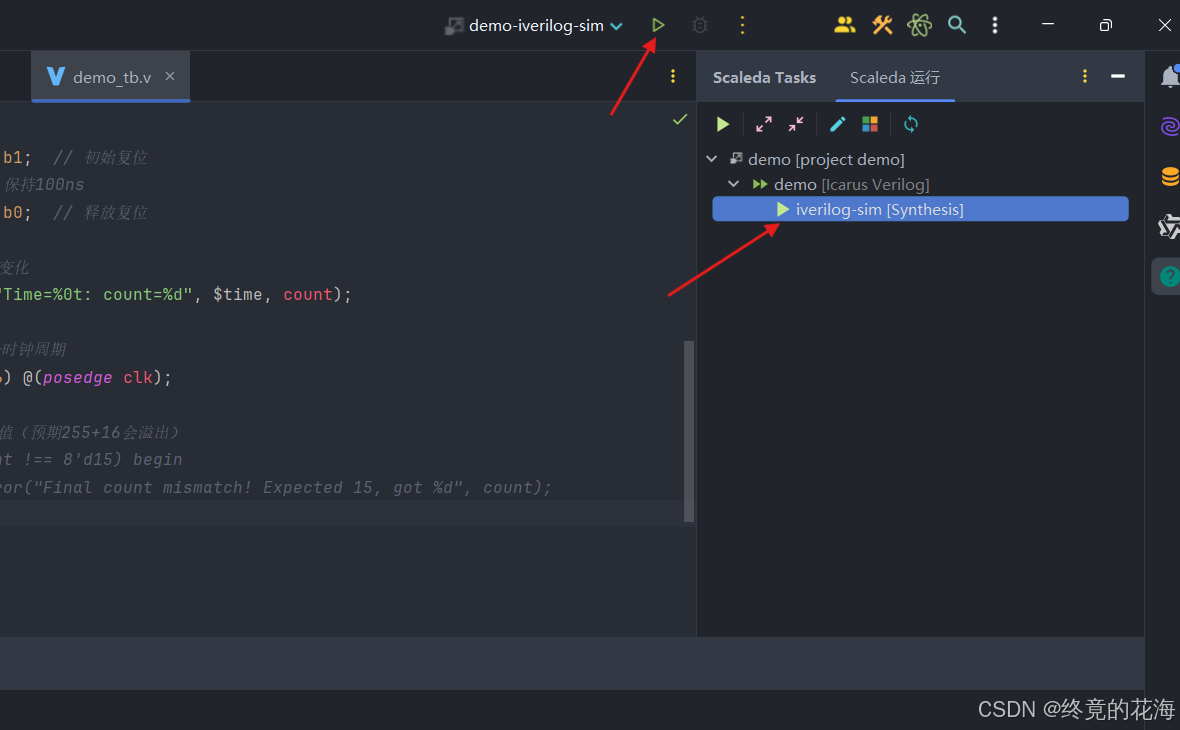

③刷新

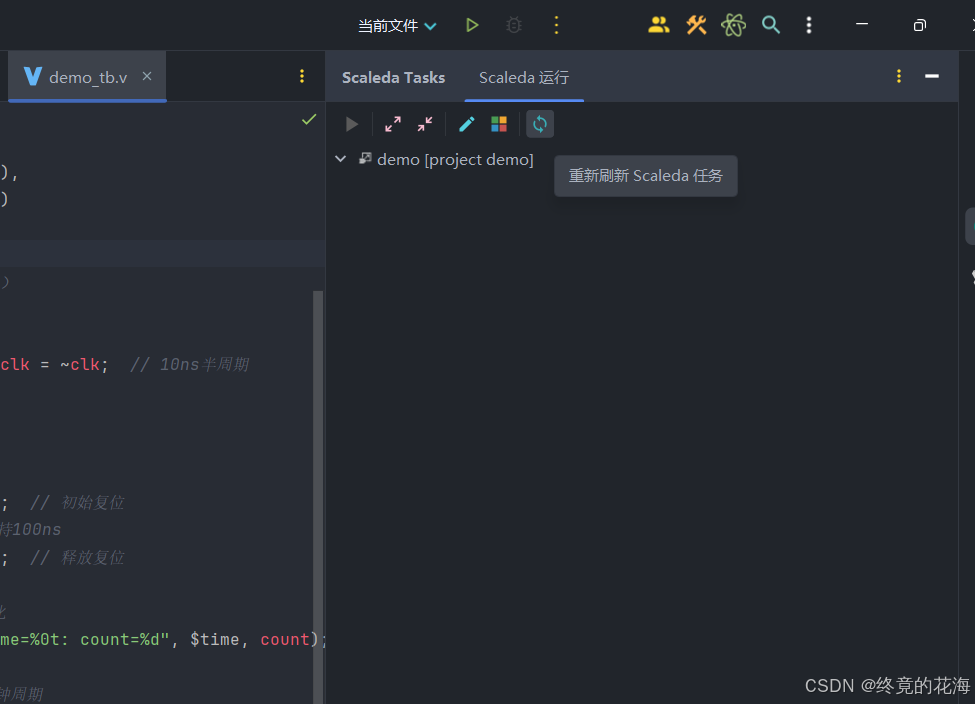

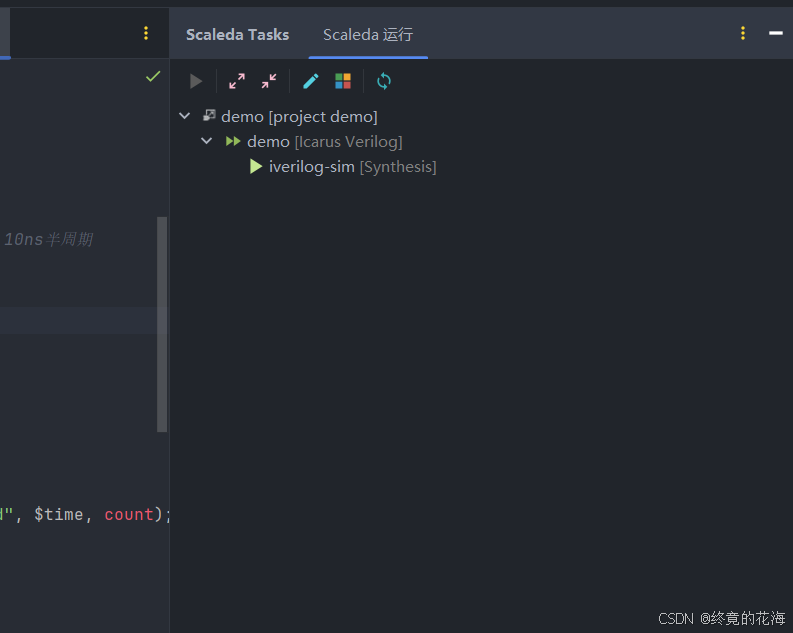

回到任务视图,点击刷新

可以看到对应配置都刷新出来了,这里方括号的显示与前面不一致,应该是个小bug

6,运行

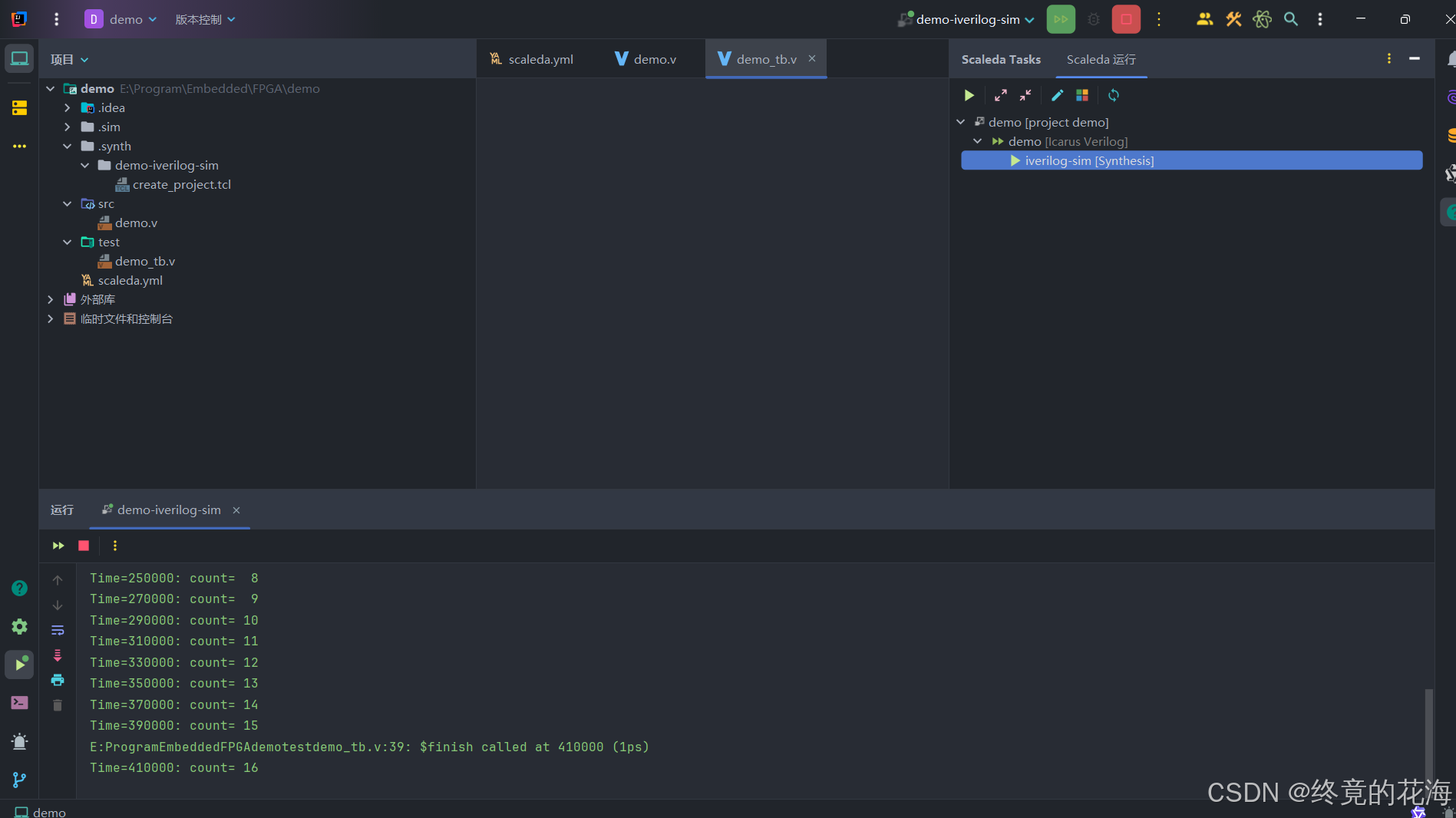

双击运行可以看到有正确的输出提示

尴尬的是,没有产生手册中的波形图

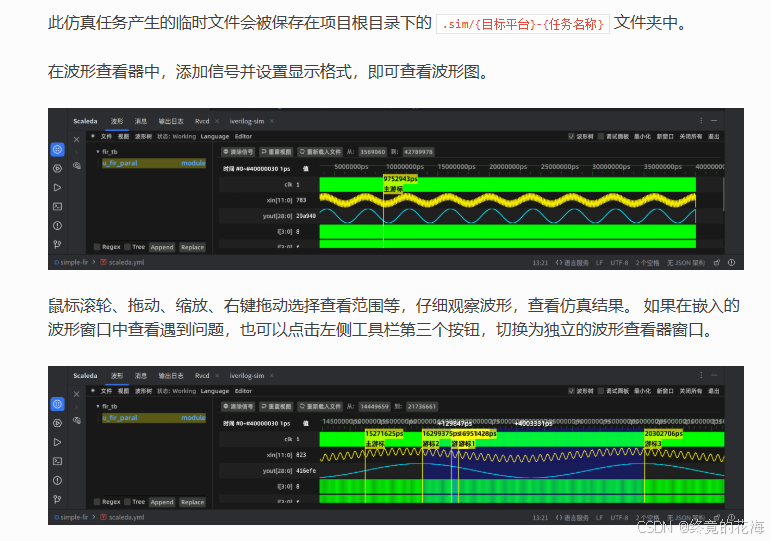

设置波形

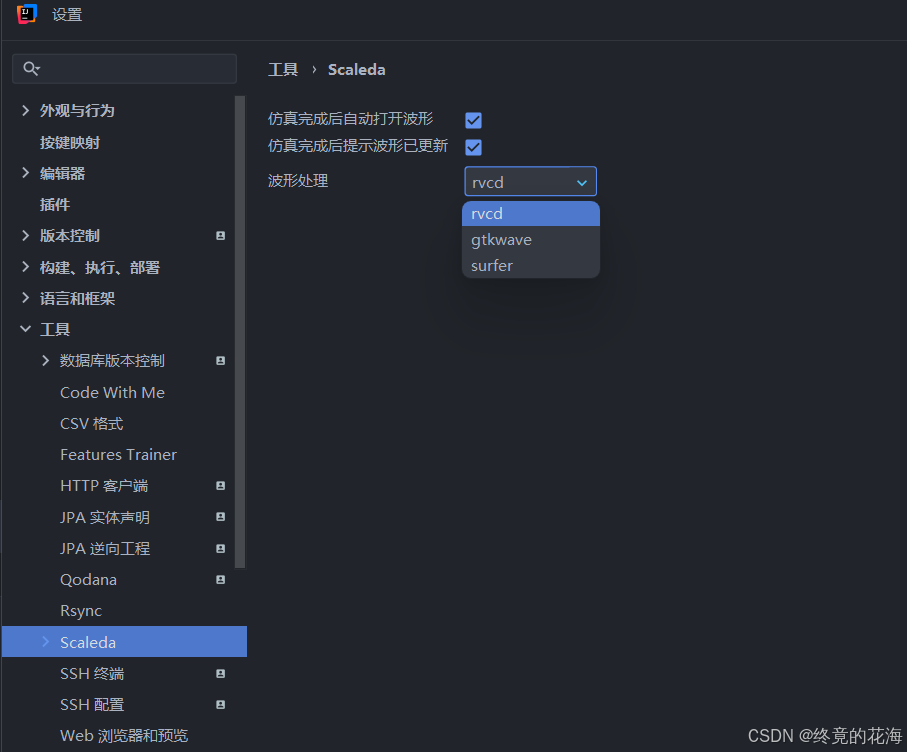

回到设置里咱去看看怎么个事。可以看到前面两个选项勾选很正常,但波形处理这块应该没有生效

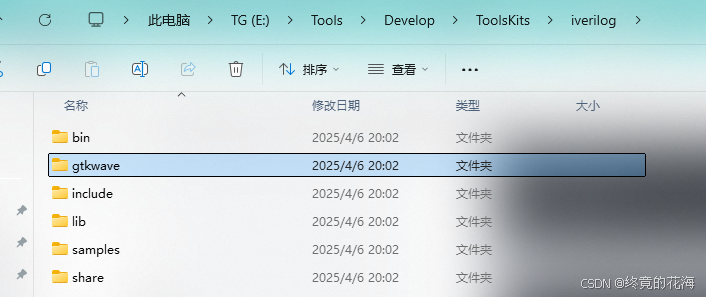

点开后,可以看到三个选项,其中gtkwave我们在iverilog的目录里看到过,那么就选择它吧

gtkwave

双击任务视图里的仿真任务,或者点击上面的运行,效果相同

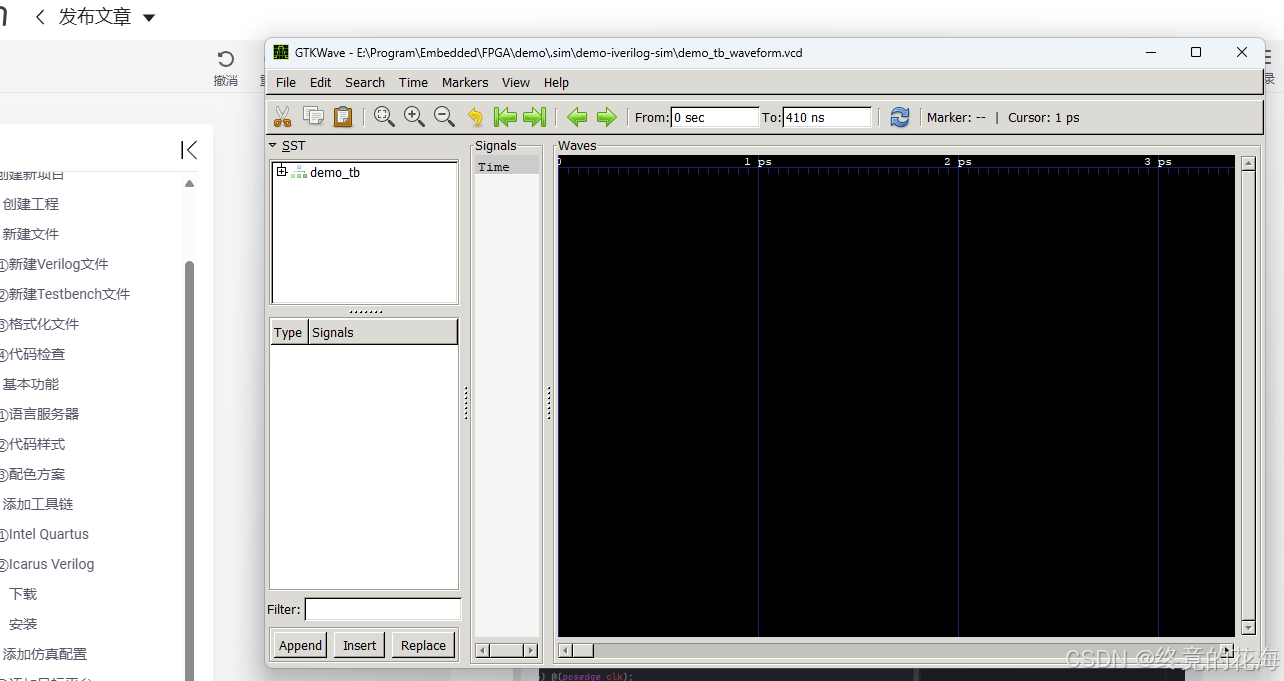

此时,会弹出一个新窗口(老窗口)

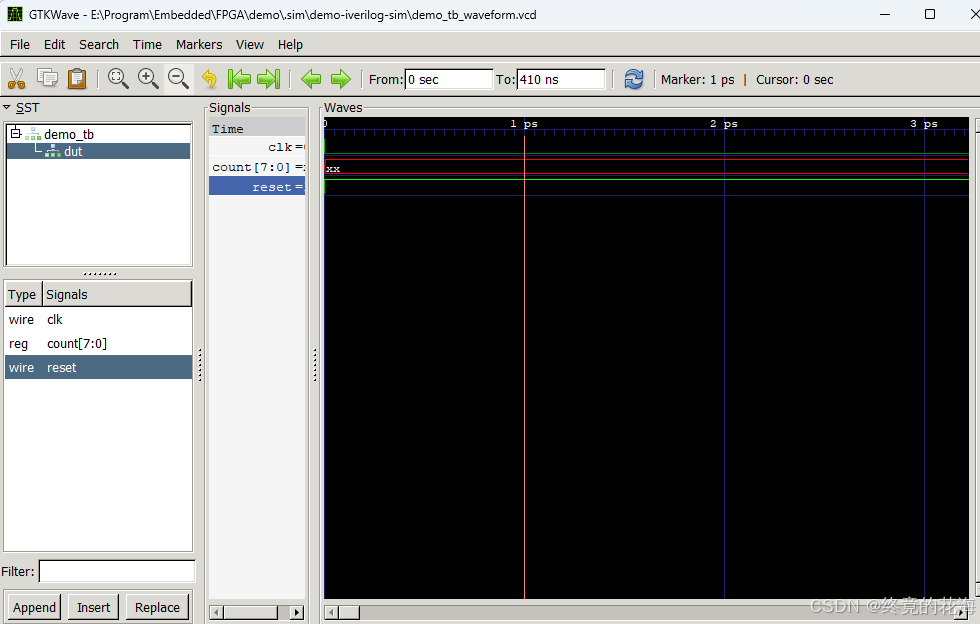

点击SST栏里的demo_tb,可以将其展开,其下方栏也会有相应信息

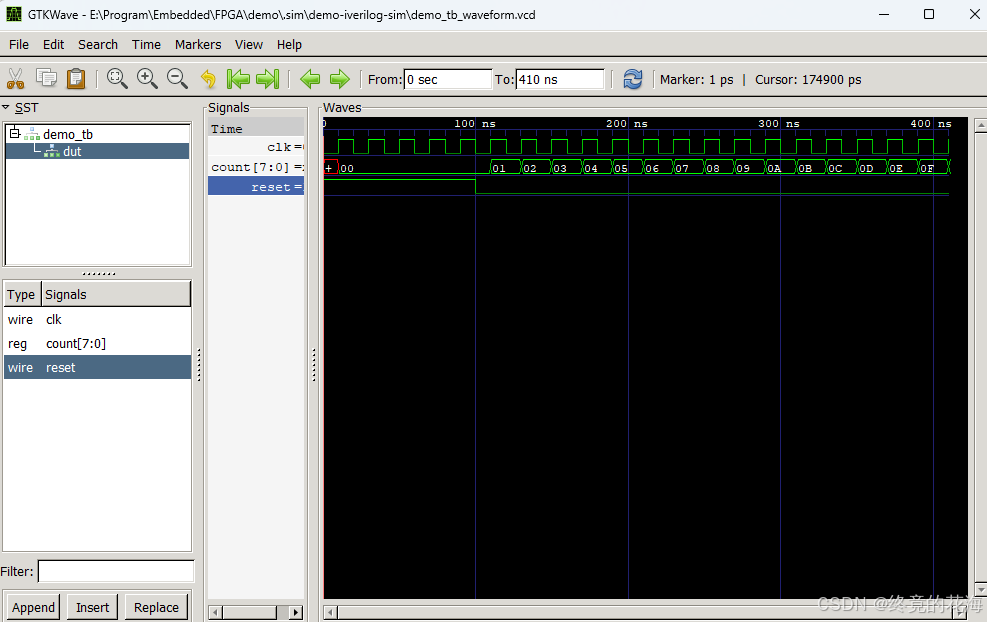

点击这些信号,Signals那一栏就会出现相应信号,Waves下则出现对应波形

缩放一下,有那么一点韵味了

Surfer

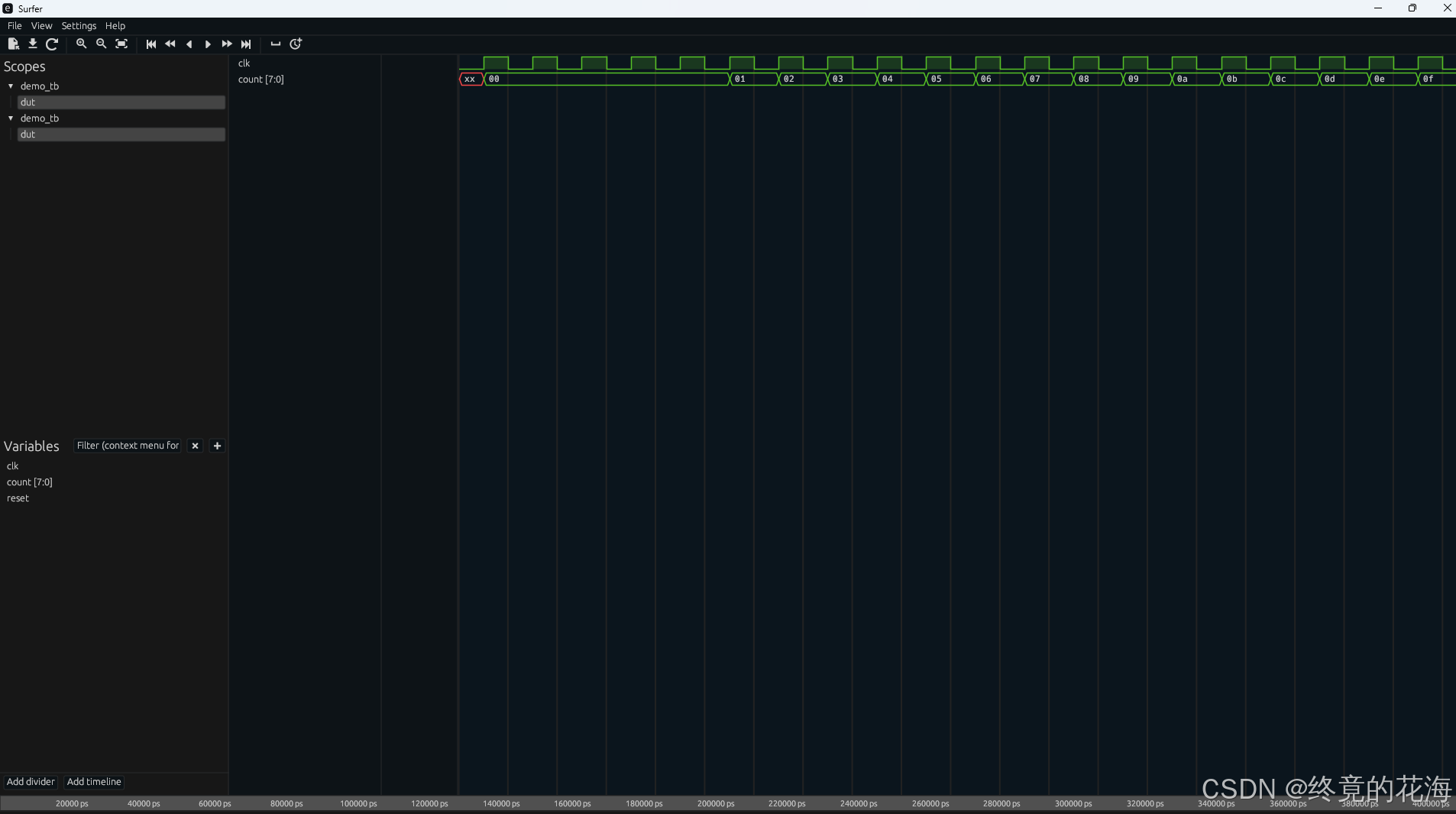

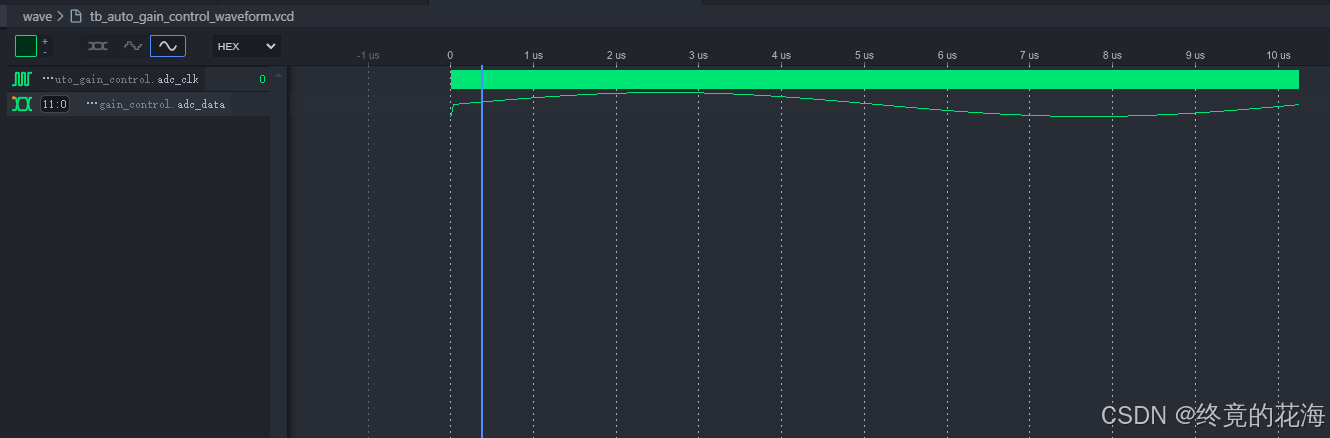

与前面相同,在设置里选择即可,点击运行后,可以弹出这样一个窗口。不得不说,这个背景色调相当有吸引力

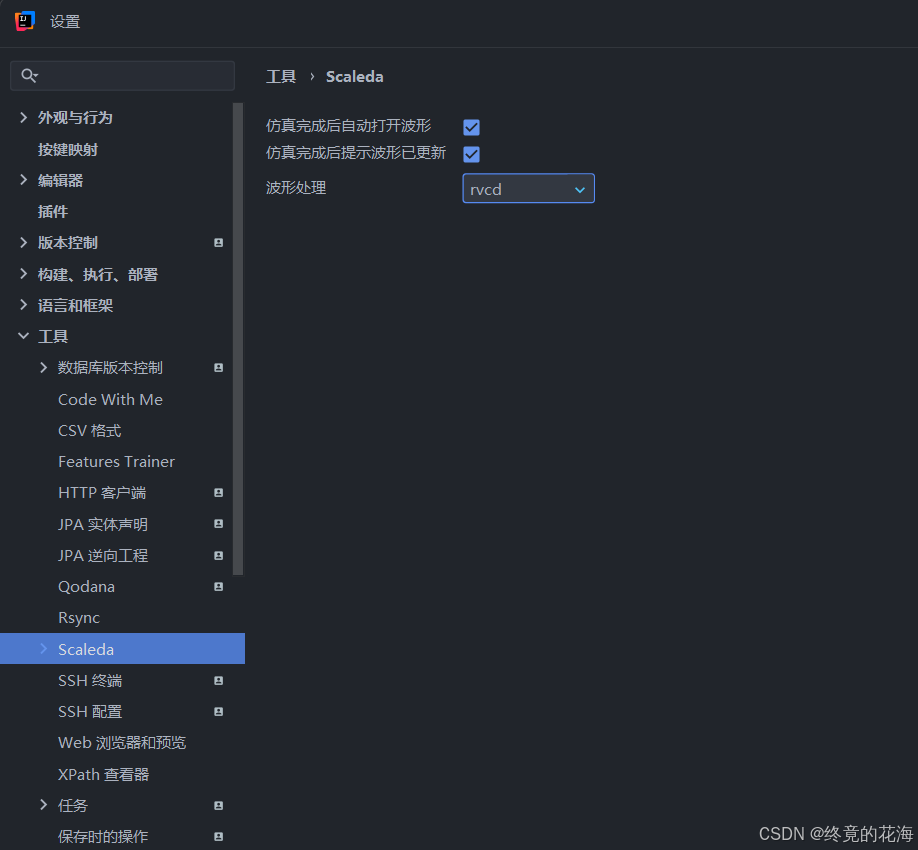

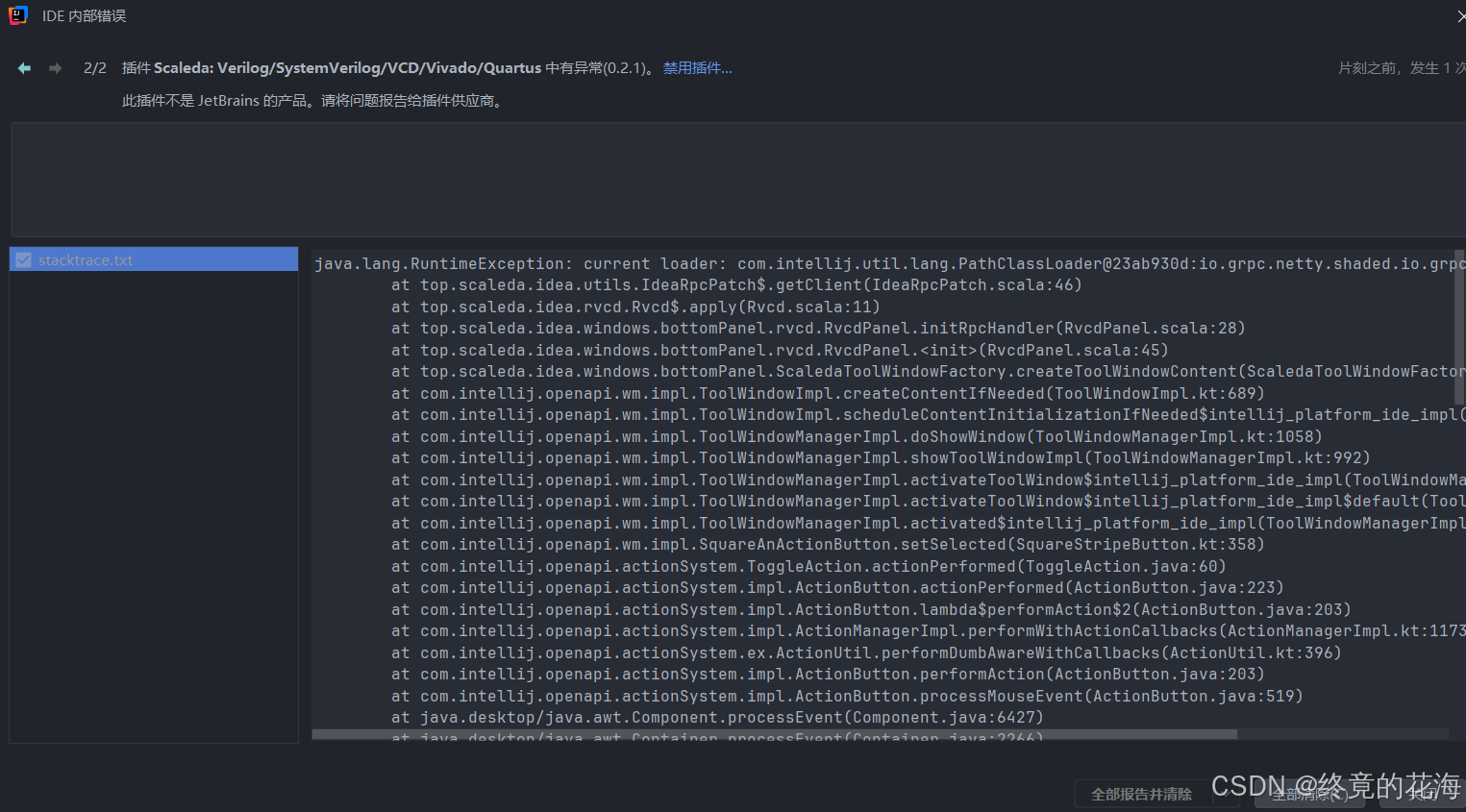

Rvcd(未解决)

虽然插件里提到,Rvcd和Surfer是内置的,不过实际运行仿真任务时Rvcd却没有任何窗口,可能是我姿势不对?

应该是插件错误导致的

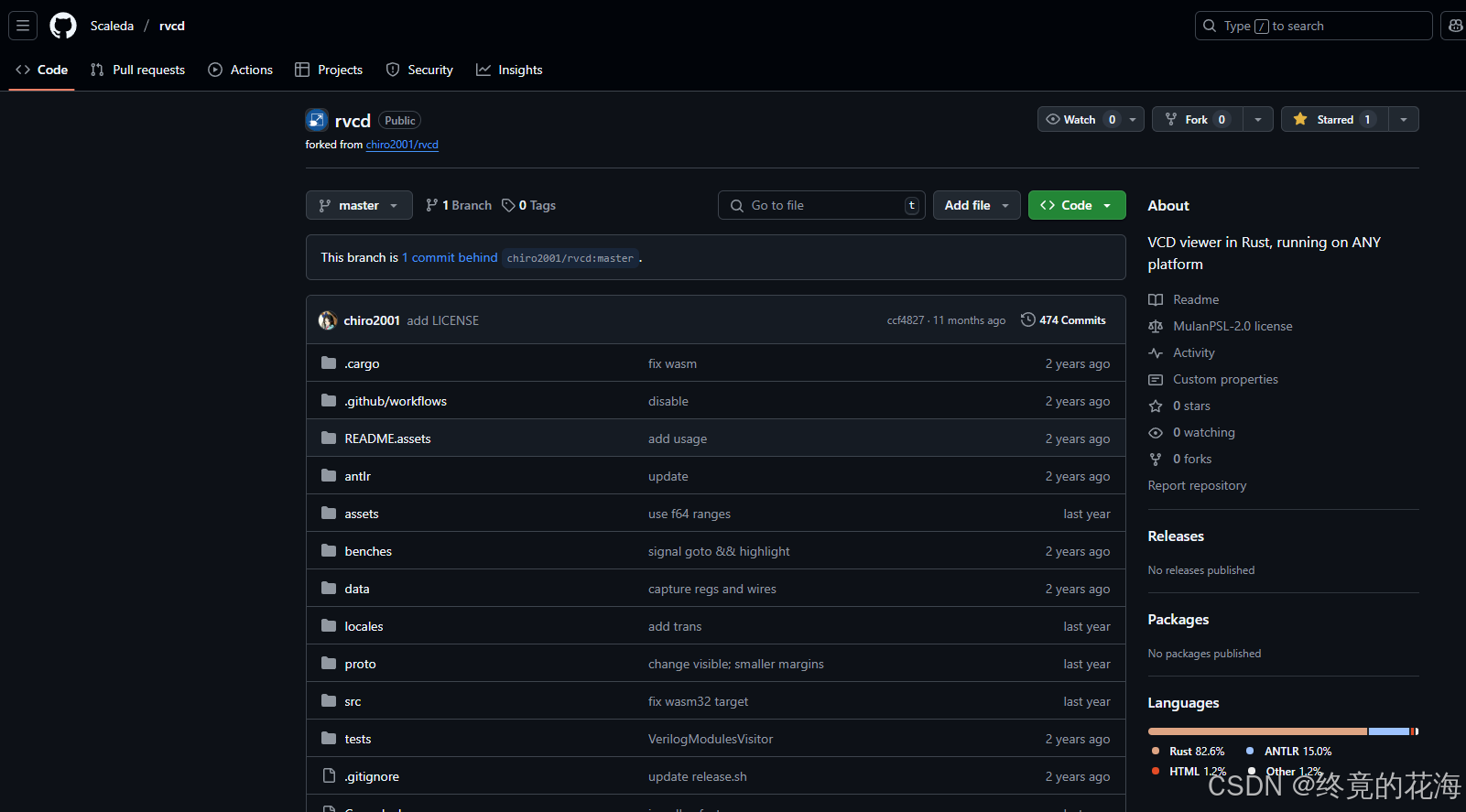

7、曲线救Rvcd(失败)

找到Rvcd项目(非常棒的项目),Scaleda/rvcd: VCD viewer in Rust, running on ANY platform

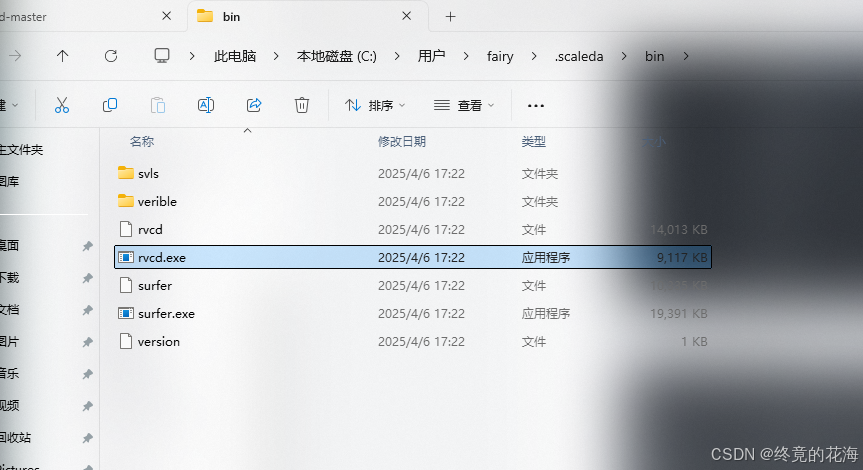

不过,我们并不需要下载Rust编译器。到设置里,我们可以看到LSP的可执行路径,那么我们就前往这个路径

在bin这里,可以找到我们想要的文件

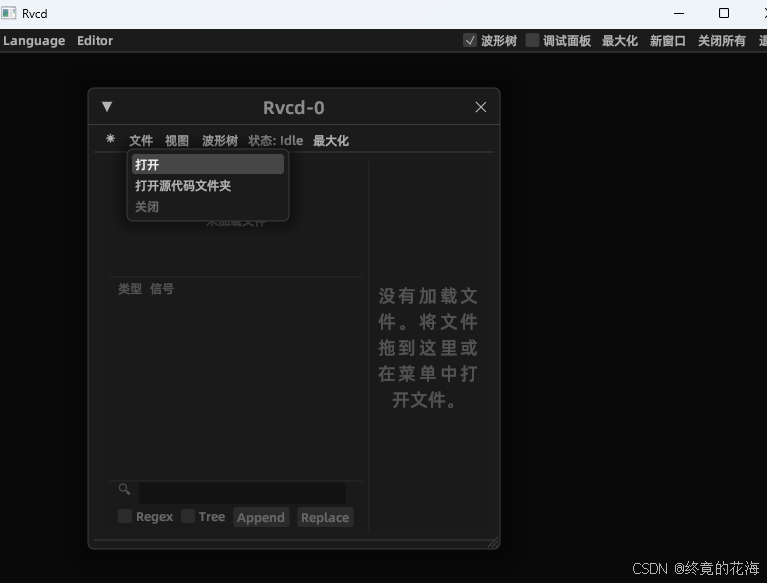

双击运行

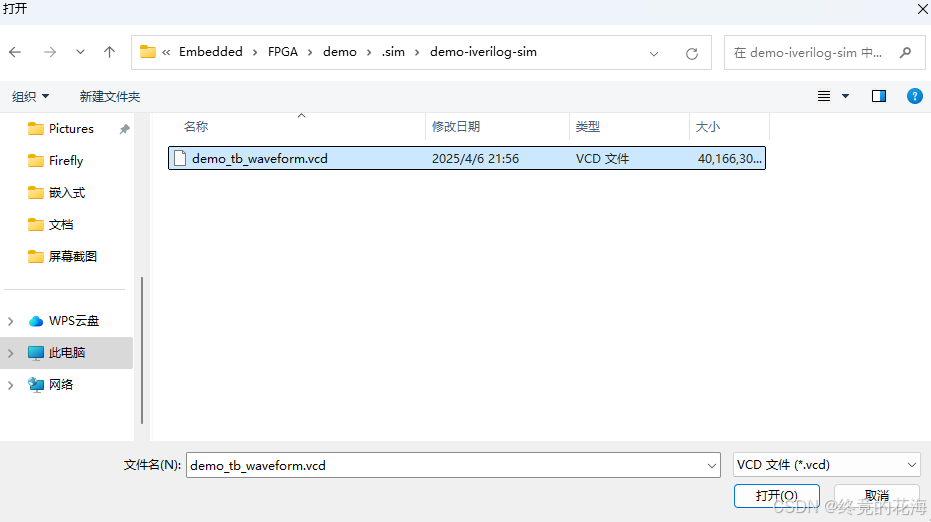

找到我们项目下的仿真波形文件

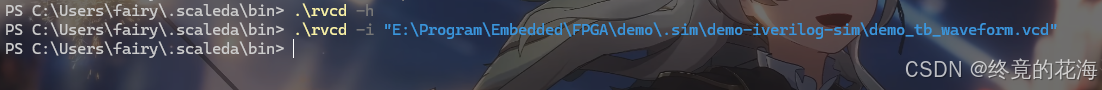

然后什么都没发生,疑似程序崩溃。那么根据README提示,使用命令行来完成操作(路径需自行替换).\rvcd -i "E:\Program\Embedded\FPGA\demo\.sim\demo-iverilog-sim\demo_tb_waveform.vcd"

刚才当我没说,Rust编译器还是得下,下载是基本功,这里不啰嗦了。下载Rvcd源码压缩包后,执行下面命令进行编译# run rvcd cargo run # compile to release executable cargo build --release

三、综合Quartus项目

1,迁移

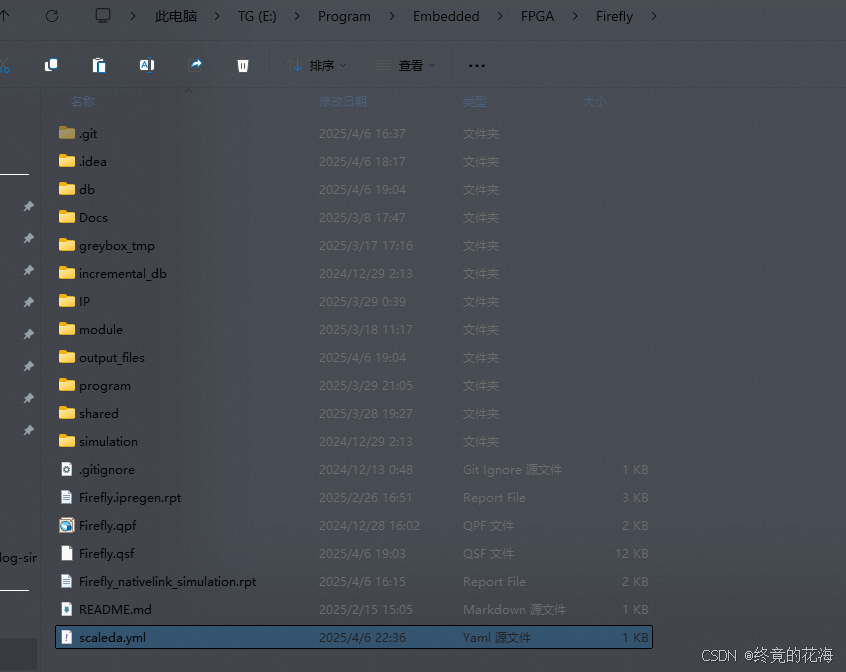

把前面工程下的scaleda.yml复制到Quartus的旧工程里

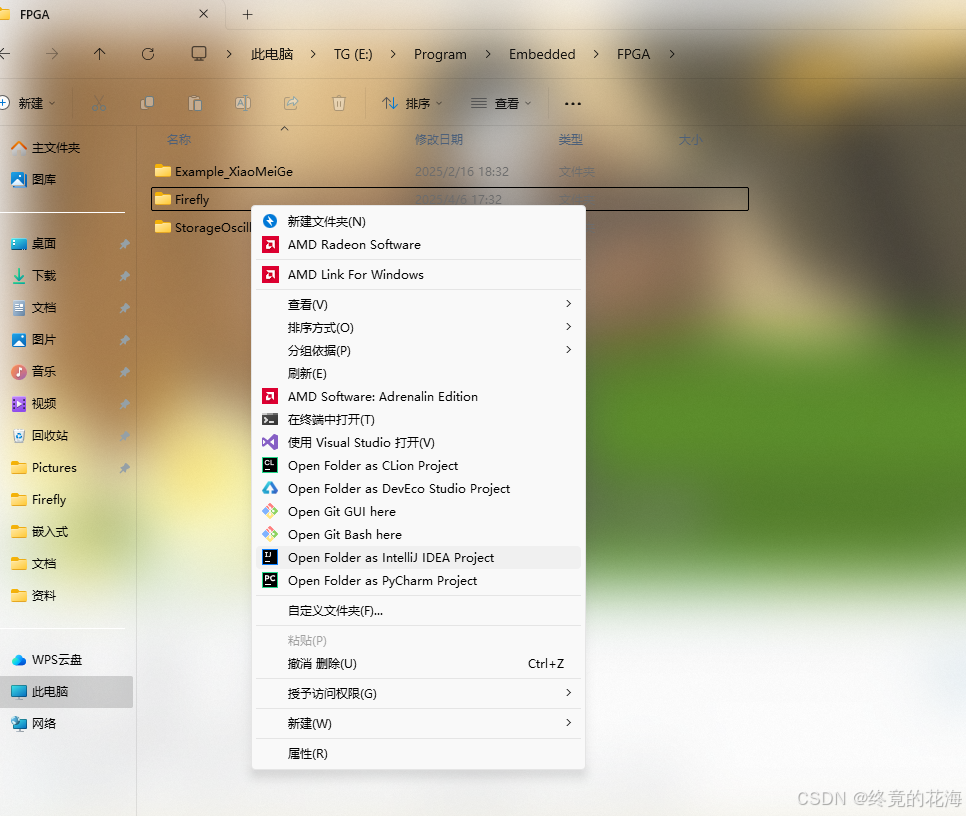

然后右键工程文件夹,使用IDEA打开

接着修改配置即可,如果配置不生效,那么就重启IDEA。可以选择在任务视图里修改,也就是图形化操作

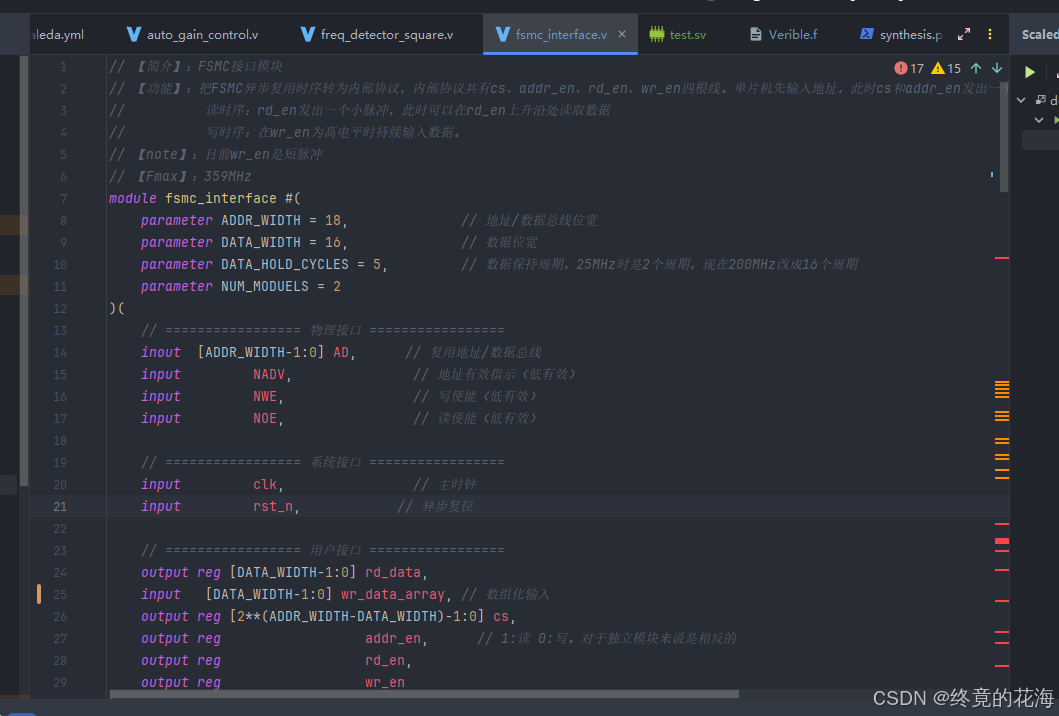

该插件对System Verilog的支持有限,建议文件后缀名为.v,使用Verilog2,原理

接下来是对项目进行综合,不知道为什么,这个插件Quartus的综合项目时只会卡着,什么反应都没有

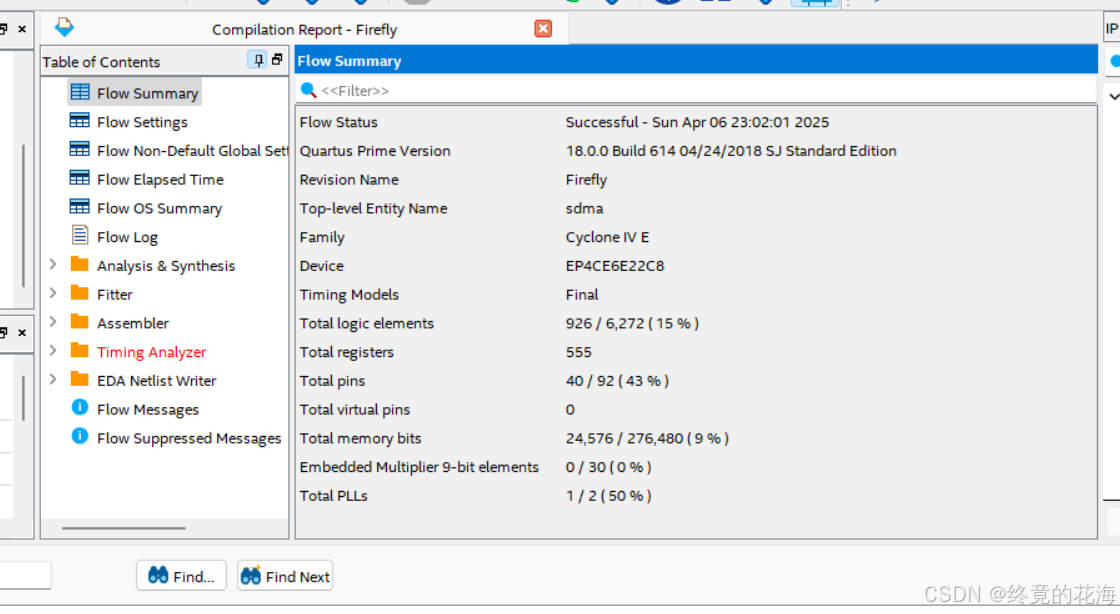

不过综合这一步终归是利用Quartus的工具,自己手动配置也没多麻烦。于是在Quartus里运行一下,进行综合。

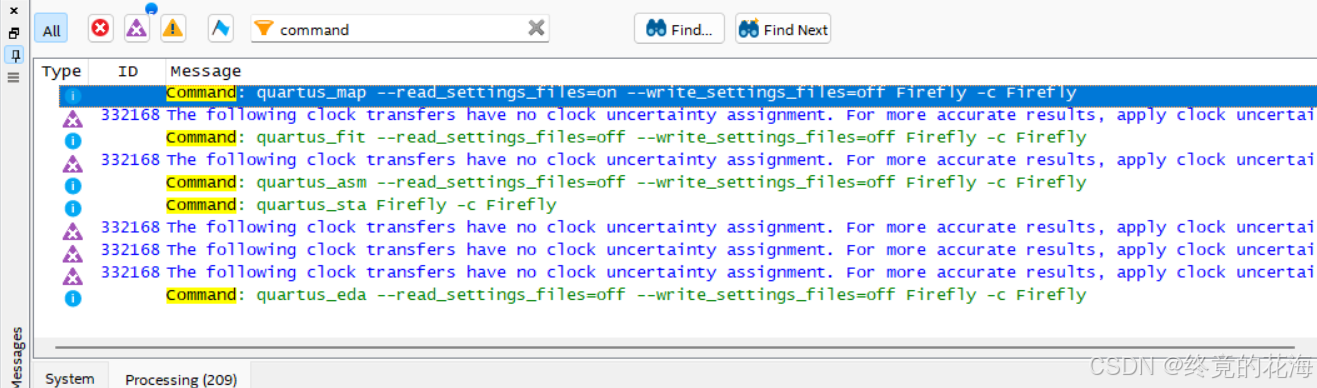

然后再根据输出信息框筛选出命令,可以看到它执行了下面的五条命令,我们只需要把这些命令添加到外部工具即可

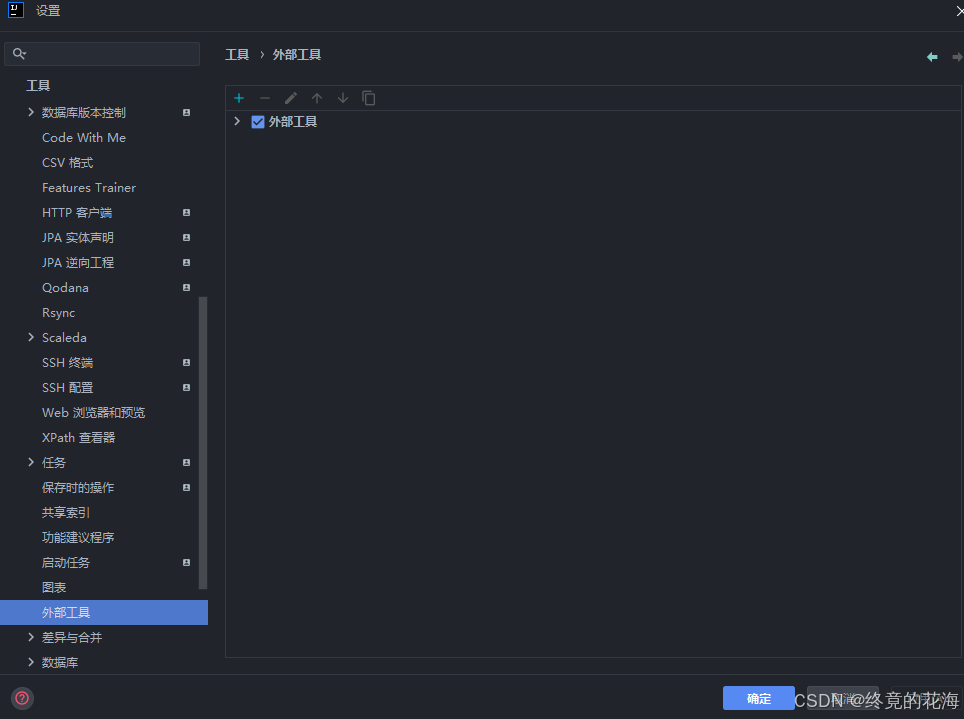

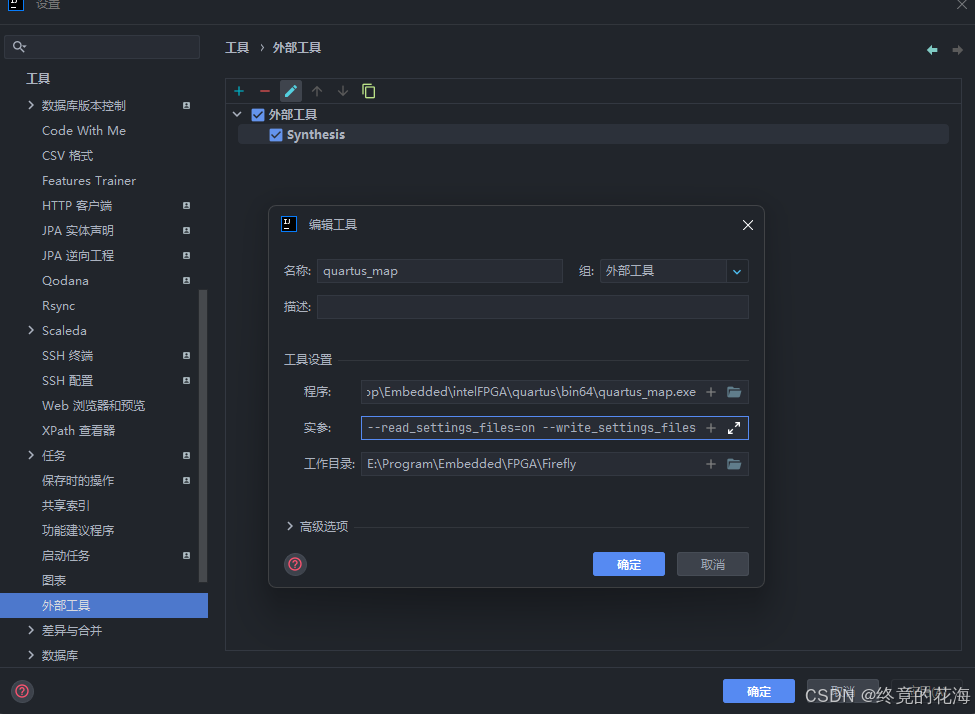

打开设置,找到外部工具,点击“+”添加外部工具

可以输入下面信息

这些信息怎么来的呢?前面在输出信息框里,我们先找第一条命令

Info: Command: quartus_map --read_settings_files=on --write_settings_files=off Firefly -c Firefly“Command:”后面的内容其实就是终端里执行的命令,quartus_map就是可执行程序,后面则是它需要的参数,也就是实参

而这个程序在哪呢?它在Quartus安装目录下的quartus/bin64目录,此目录就是Intel Quartus的工具链路径。因此程序一栏添该程序的完整执行路径即可

我们需要编译(综合)本工程,那么工作目录自然是当前目录(项目根目录)

剩下的外部工具皆是如此配置,幸运的是工作目录和实参都差不多,只有程序名称不同。不过这种方法有些劣质,如果是不同的工程,那么工作目录就需要重新改了

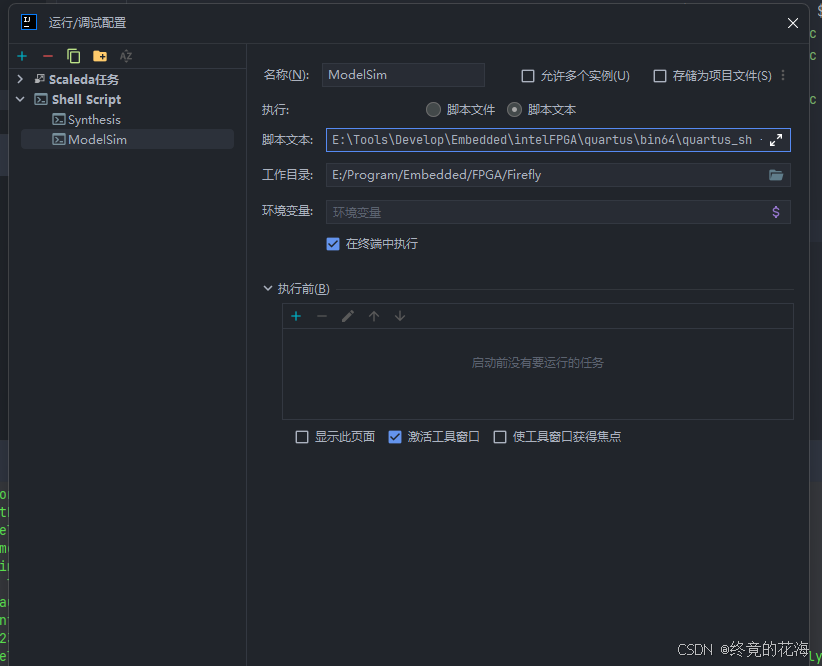

2,powershell目标

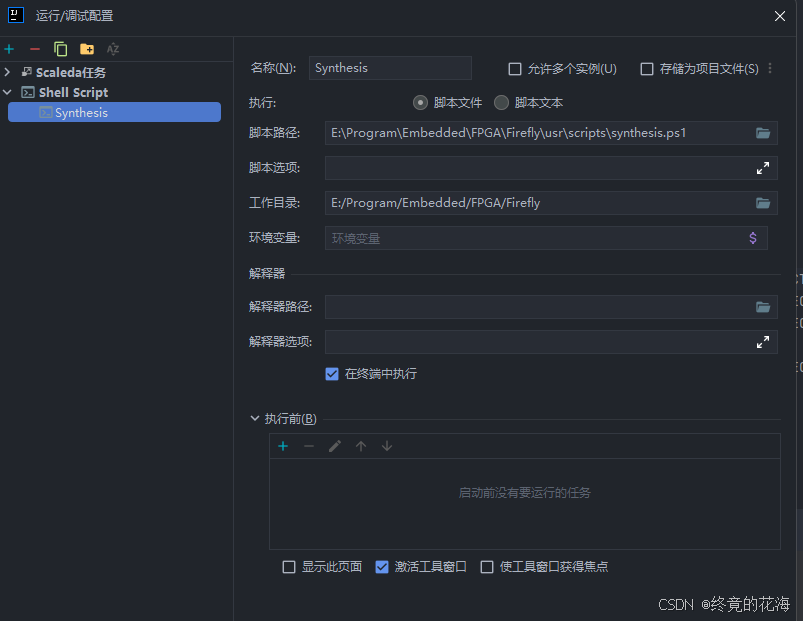

为此,干脆写一个powershell脚本,创建一个powershell目标,进行一键综合。

点击添加目标,选择Shell Script

接下来找一个目录存放脚本

可根据自己的情况更改

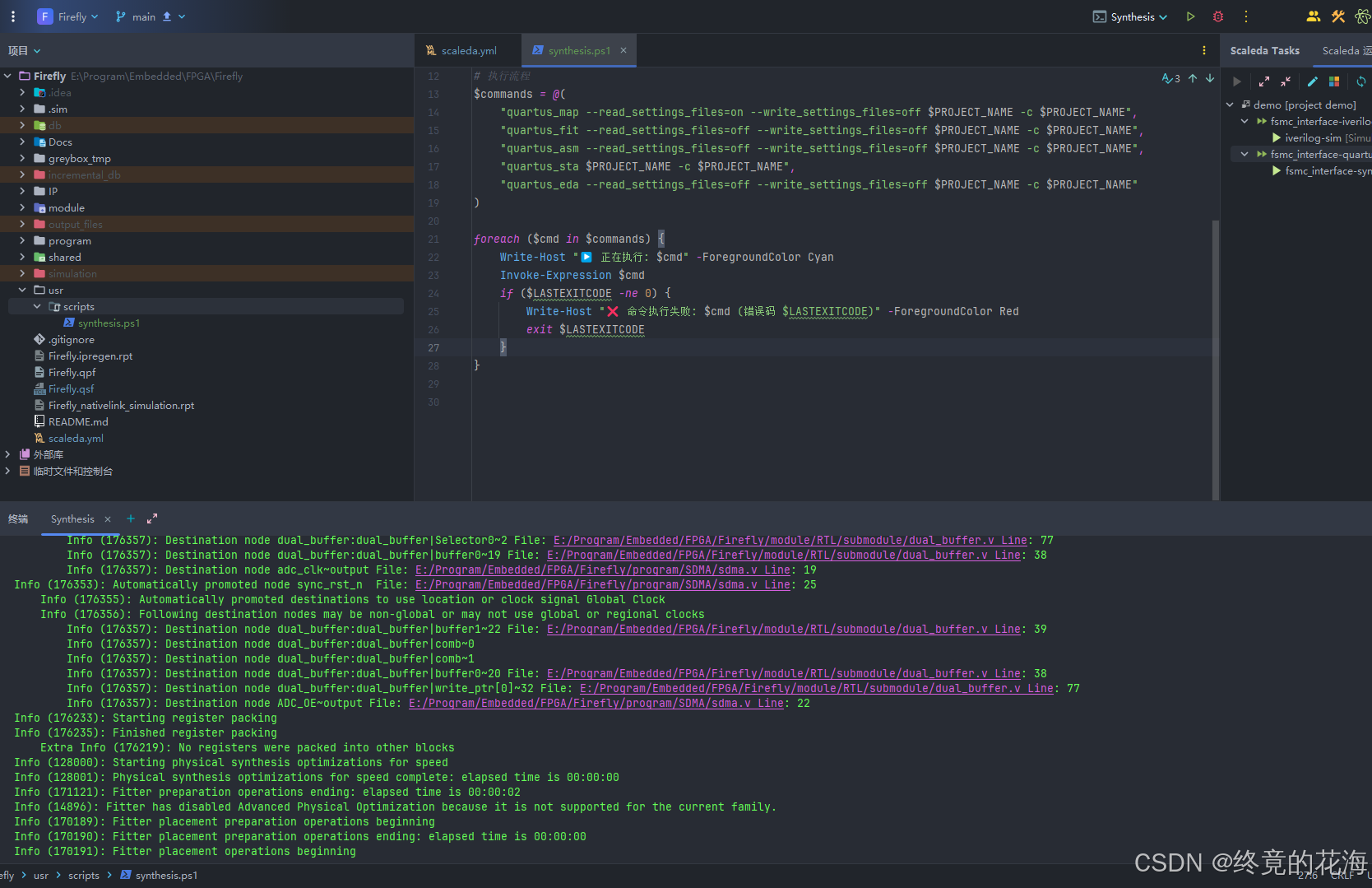

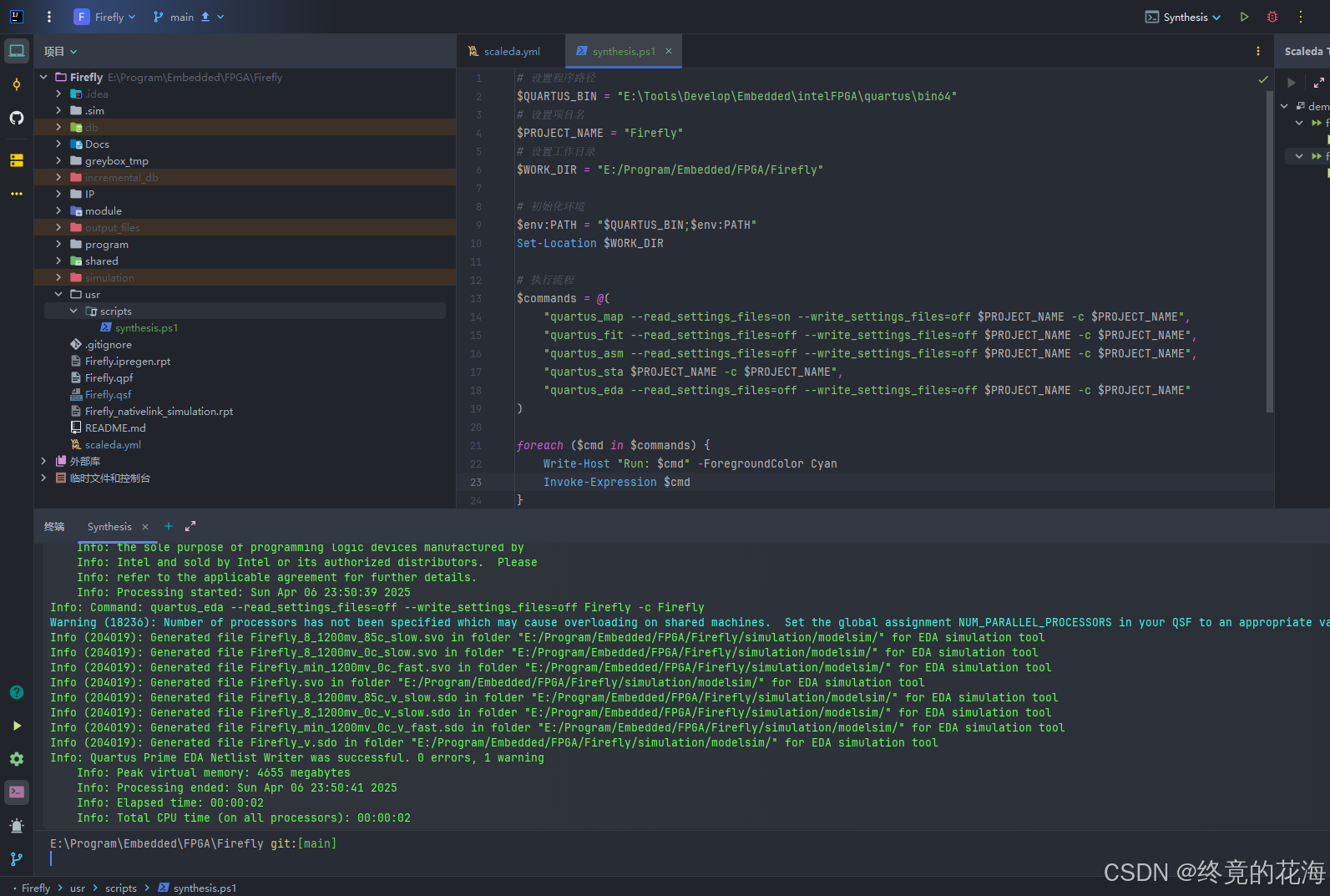

# 设置程序路径 $QUARTUS_BIN = "E:\Tools\Develop\Embedded\intelFPGA\quartus\bin64" # 设置项目名 $PROJECT_NAME = "Firefly" # 设置工作目录 $WORK_DIR = "E:/Program/Embedded/FPGA/Firefly"# 初始化环境 $env:PATH = "$QUARTUS_BIN;$env:PATH" Set-Location $WORK_DIR# 执行流程 $commands = @("quartus_map --read_settings_files=on --write_settings_files=off $PROJECT_NAME -c $PROJECT_NAME","quartus_fit --read_settings_files=off --write_settings_files=off $PROJECT_NAME -c $PROJECT_NAME","quartus_asm --read_settings_files=off --write_settings_files=off $PROJECT_NAME -c $PROJECT_NAME","quartus_sta $PROJECT_NAME -c $PROJECT_NAME","quartus_eda --read_settings_files=off --write_settings_files=off $PROJECT_NAME -c $PROJECT_NAME" )foreach ($cmd in $commands) {Write-Host "Run: $cmd" -ForegroundColor CyanInvoke-Expression $cmdif ($LASTEXITCODE -ne 0) {Write-Host "[Error] $LASTEXITCODE" -ForegroundColor Redexit $LASTEXITCODE} }此时在目标里填上脚本路径,把解释器路径清空

执行目标后,输出结果与Quartus相同,除了最后一条总结外

这里只是提供了一种可行性的方案,进行综合还是要到Quartus里。至于烧录等操作,则同理

3,编写项目(重要)

如果以前有项目时要非常注意,该插件对System Verilog的支持有些问题。试过许多次,最后发现,代码里不能出现中文等非ASCII字符,否则打开即崩。但它对V文件相当宽容

这就有些难办了,既想使用System Verilog,又不能写中文注释

[Crash] Verible LSP fails to open .sv files with non-ASCII characters (e.g. Chinese comments) in IntelliJ IDEA考虑到Verilog下的代码提示和代码样式明显更好,Verilog就Verilog吧

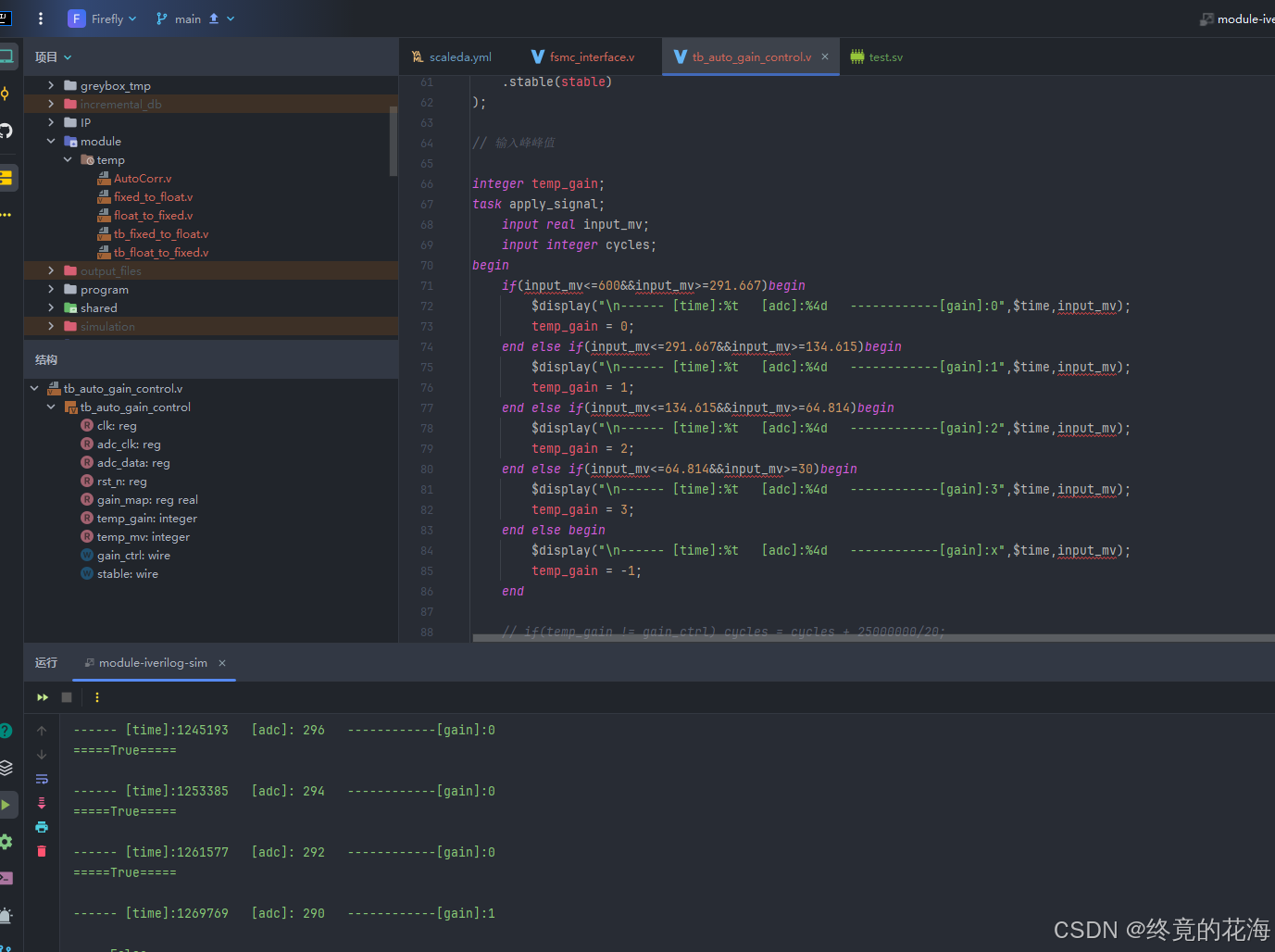

4,仿真

该插件对仿真的支持可谓差的一塌糊涂,主要是无法对sv文件进行仿真,如$sin、real、break等常见特性根本用不了。这个有空看看有没有平替或者次替

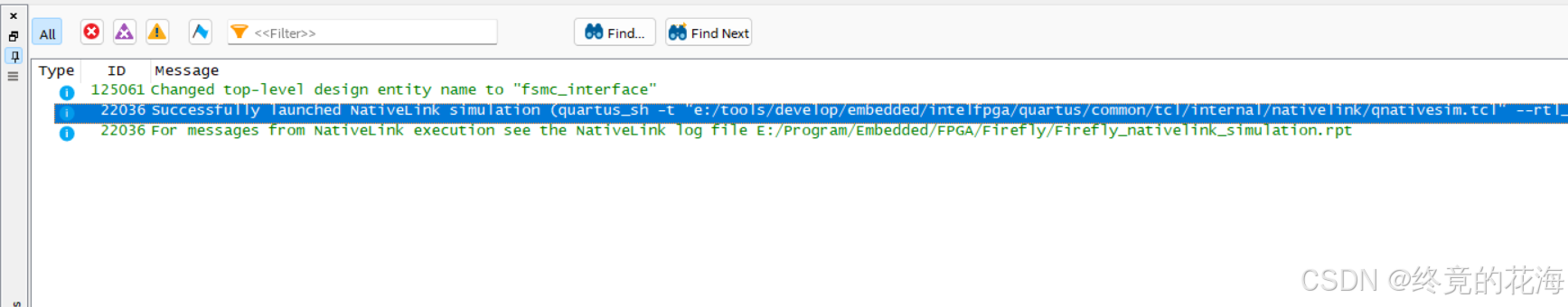

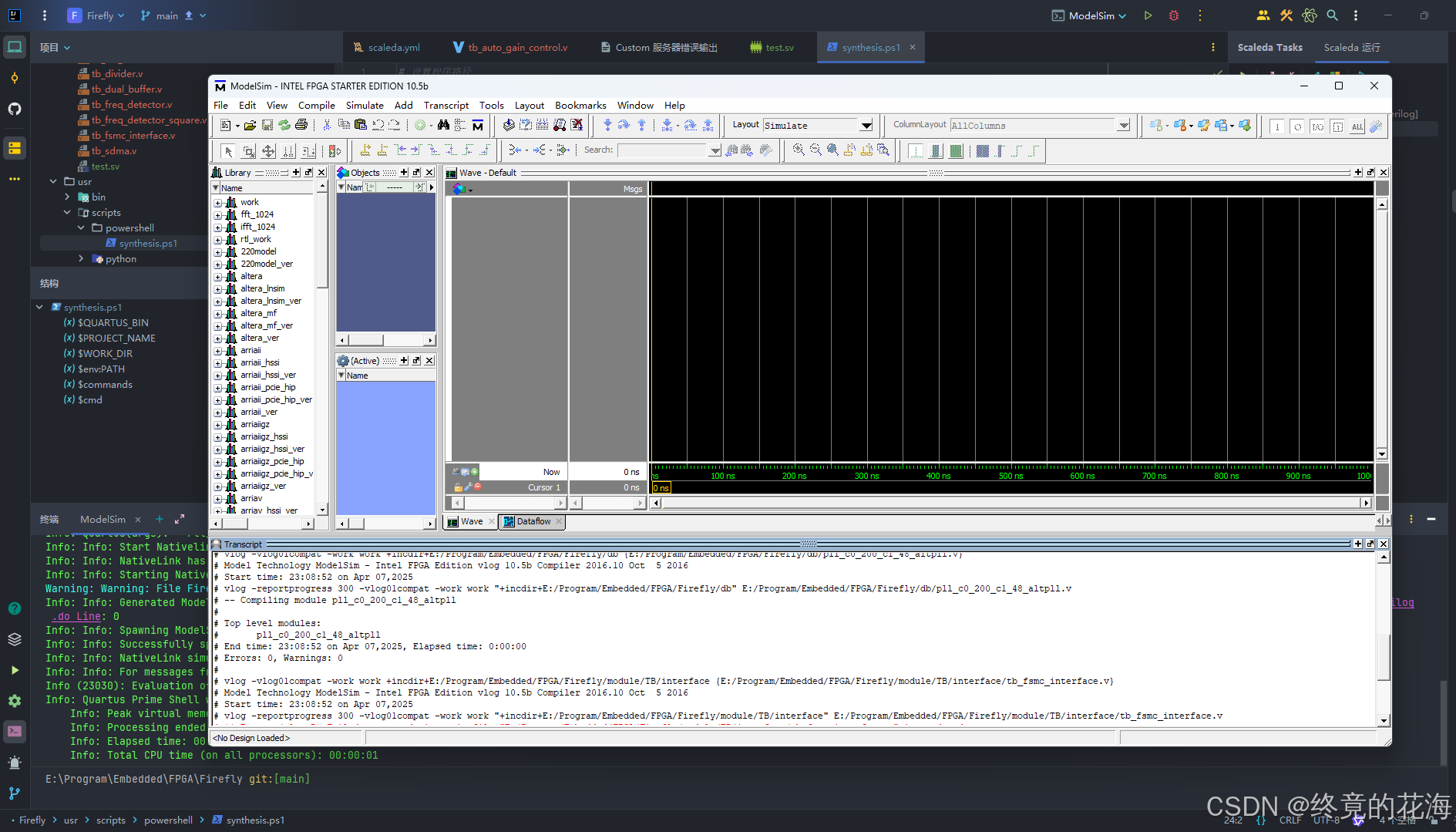

ModelSim(GUI)

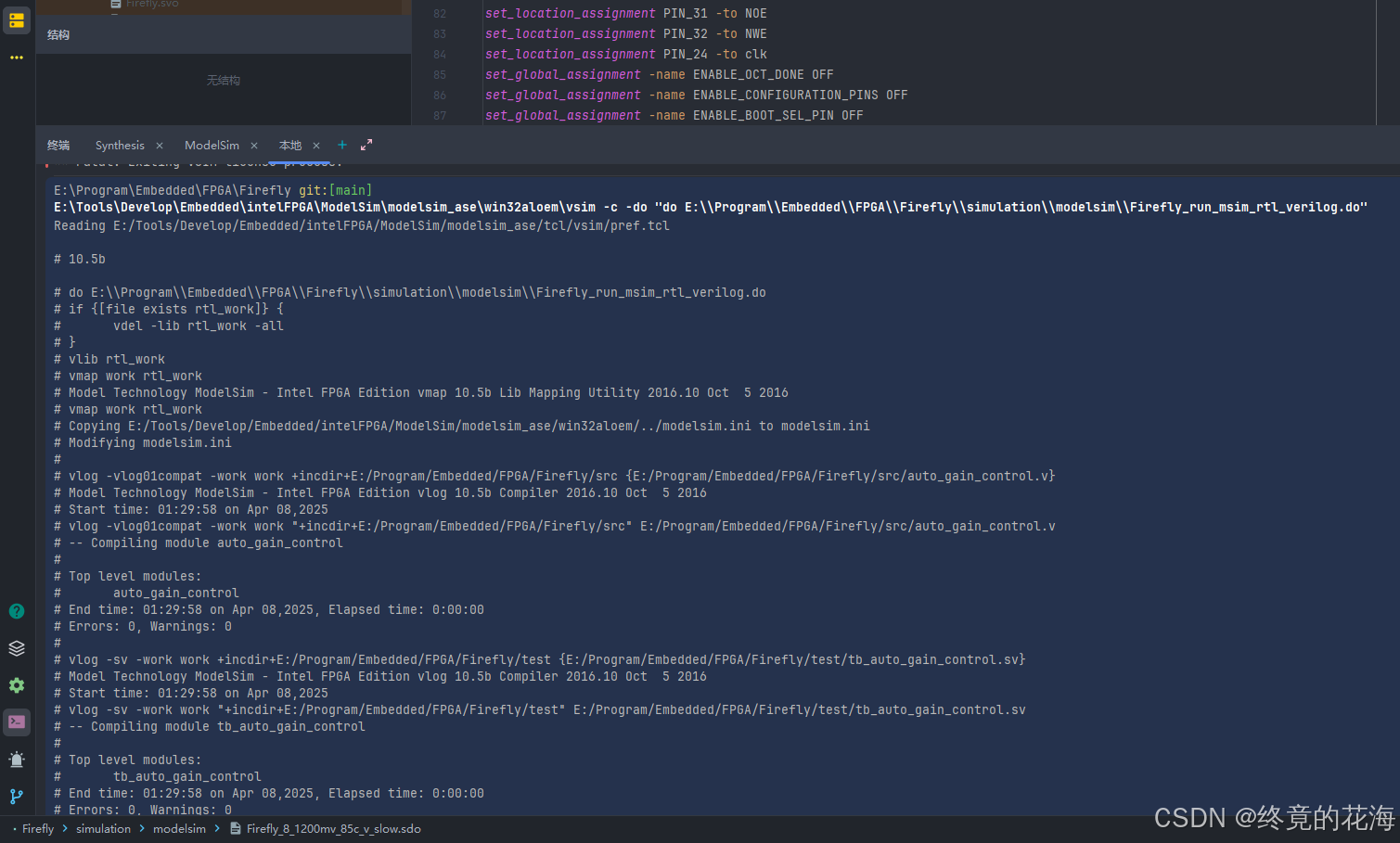

与前面综合一致,仿真时,在Quartus的输出信息框里找命令。可以看到在打开ModelSim后,输出框里有这样一条信息

而括号内的就是我们需要的命令

quartus_sh -t "e:/tools/develop/embedded/intelfpga/quartus/common/tcl/internal/nativelink/qnativesim.tcl" --rtl_sim "Firefly" "Firefly"由于命令比较简单,改为脚本文本,同时加上quartus_sh的路径

E:\Tools\Develop\Embedded\intelFPGA\quartus\bin64\quartus_sh -t "e:/tools/develop/embedded/intelfpga/quartus/common/tcl/internal/nativelink/qnativesim.tcl" --rtl_sim "Firefly" "Firefly"

运行后会自动启动ModelSim,与前面执行仿真任务Surfer差不多,唯一的区别就是,它的仿真是根据Quartus自带的tcl脚本实现的

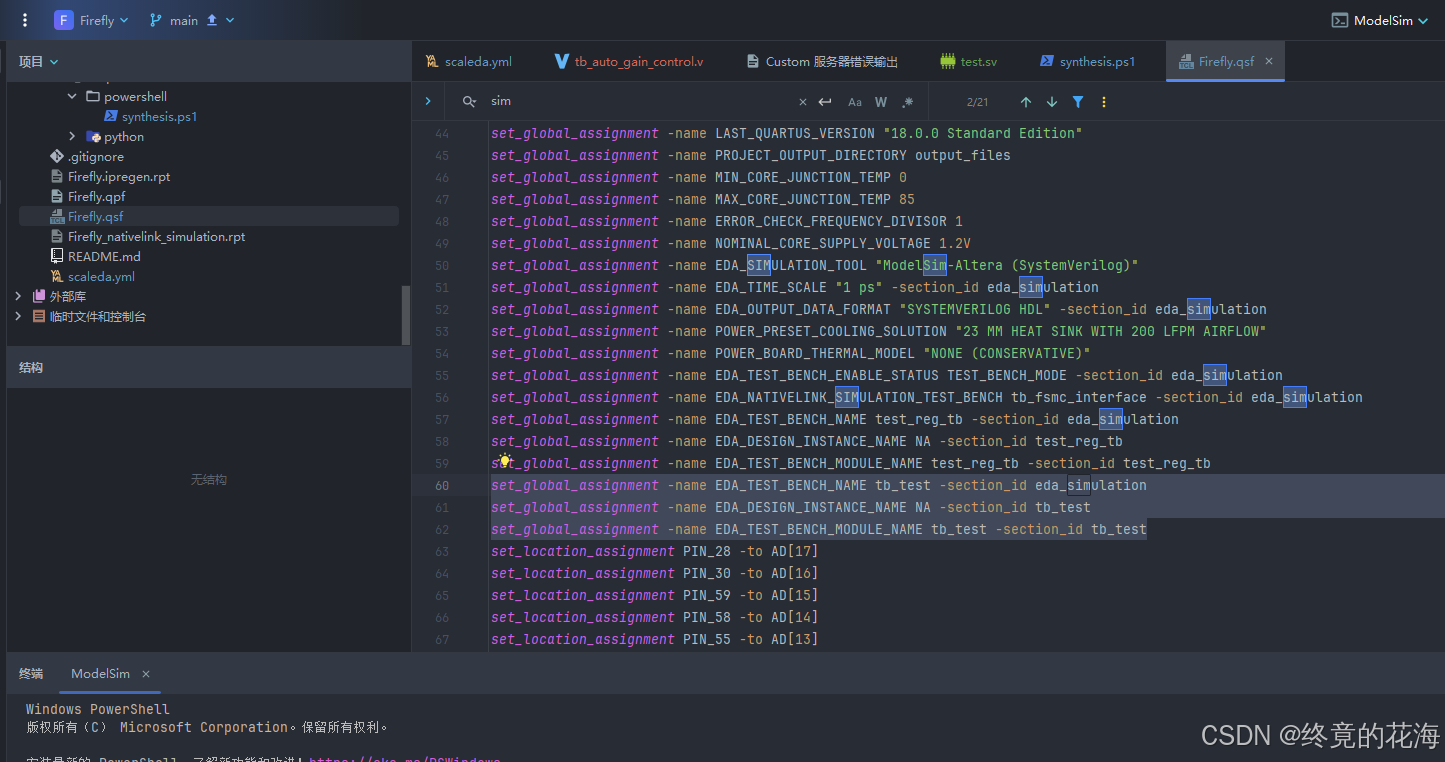

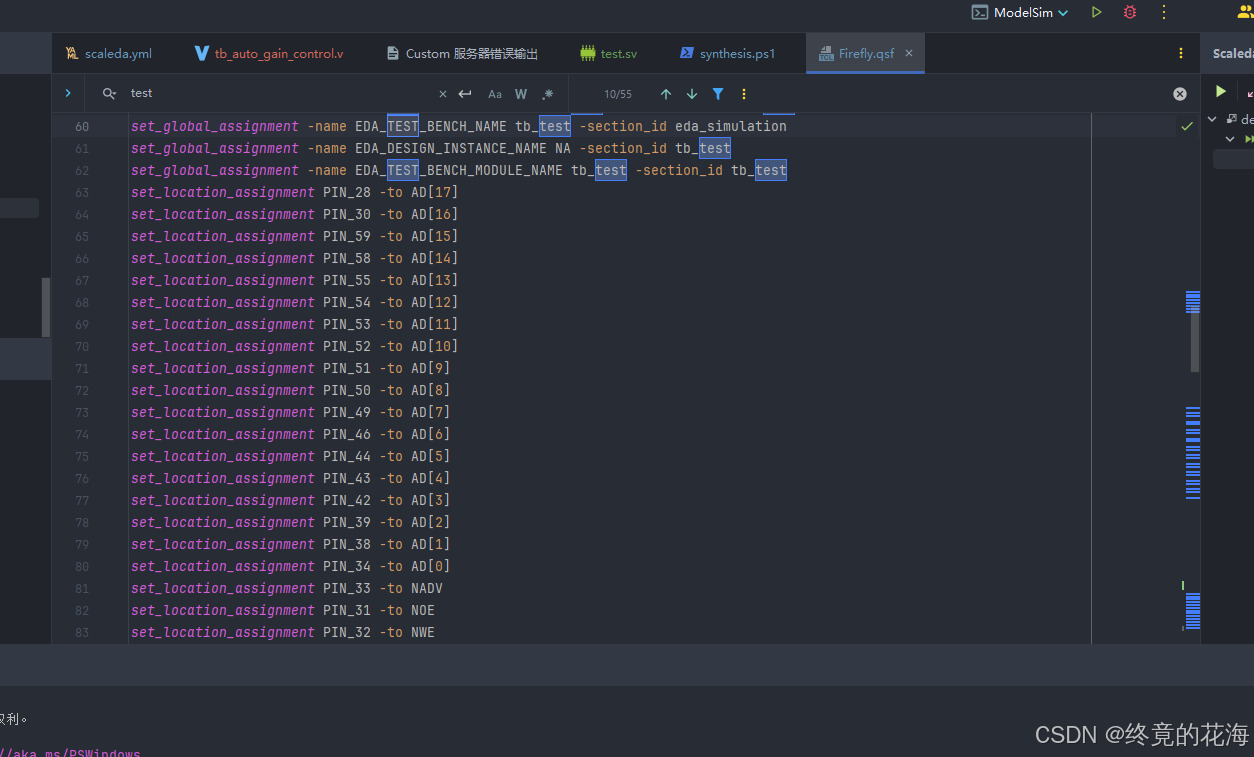

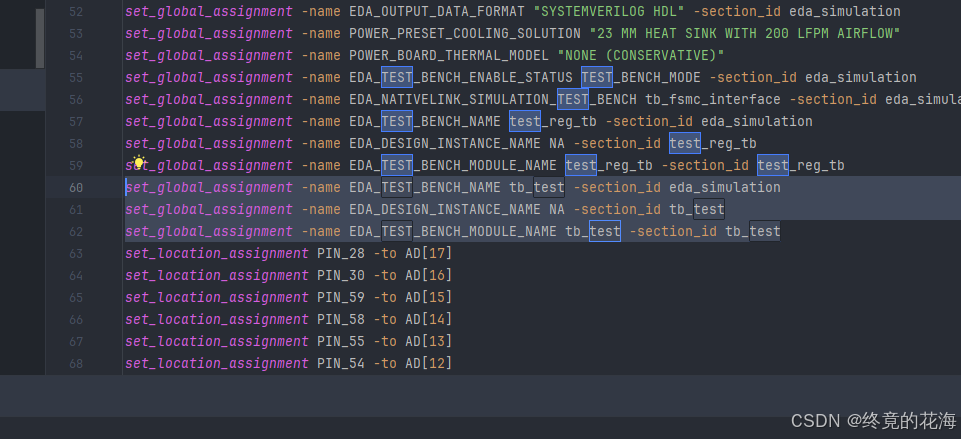

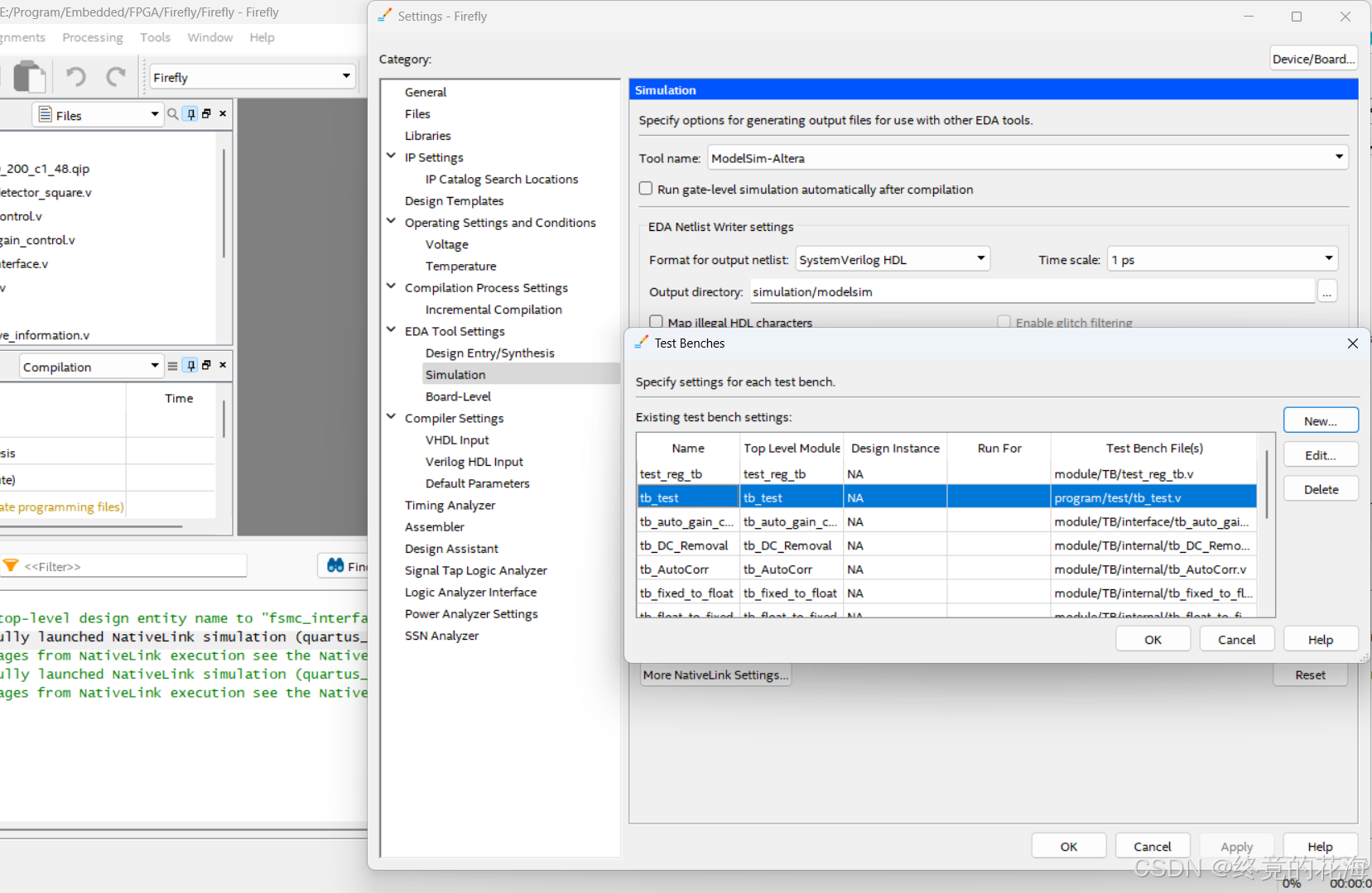

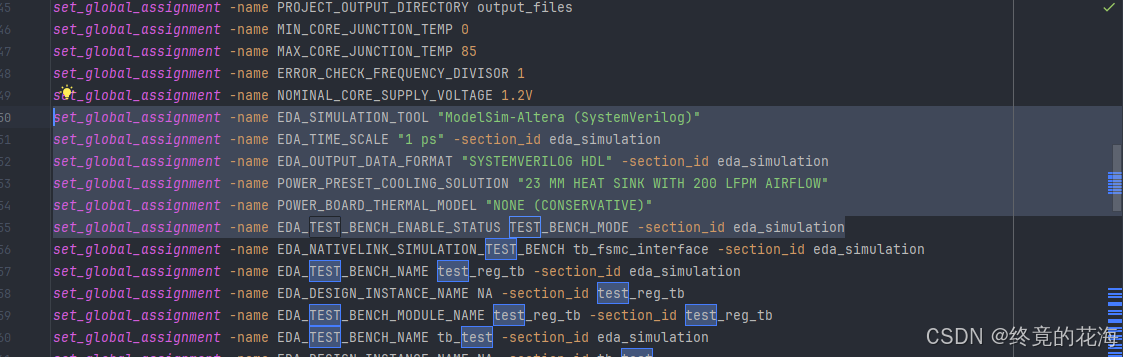

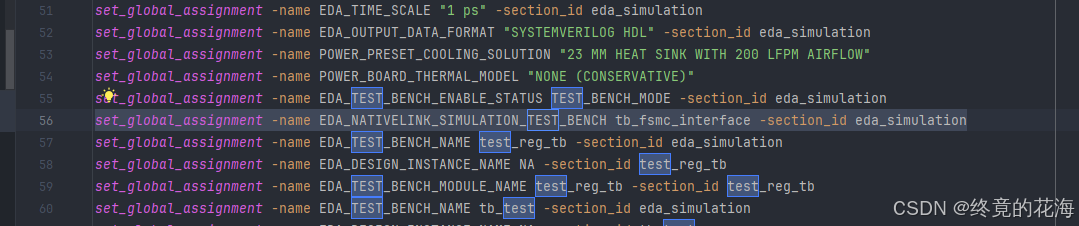

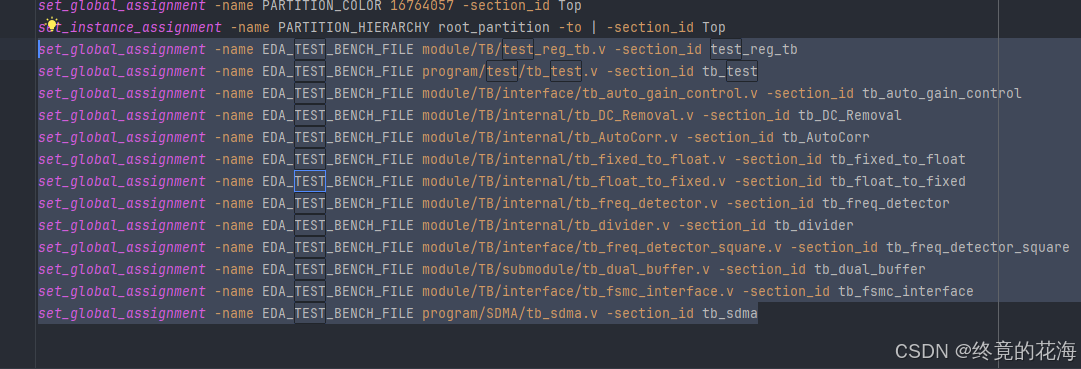

而内置的tcl脚本与qsf文件有关,换句话说,打开qsf文件,我们可以看到相关的约束命令

qsf的仿真解析

在qsf文件中,搜索test,右边蓝色区域可以就是所有涉及到测试激励(仿真)的地方

这三句对应的是图形后操作后保存的信息

这几条是仿真器的配置

这条是正在仿真的文件

这几条就是把测试激励模块与实际文件对应起来,用的是相对路径

知道这些信息后,可以很轻松地手动修改。事实上,测试激励文件的相关操作在配置文件里修改要比图形化添加要方便一些。

需要注意的是ModelSim仿真前,需要进行综合,也就是前面那个目标

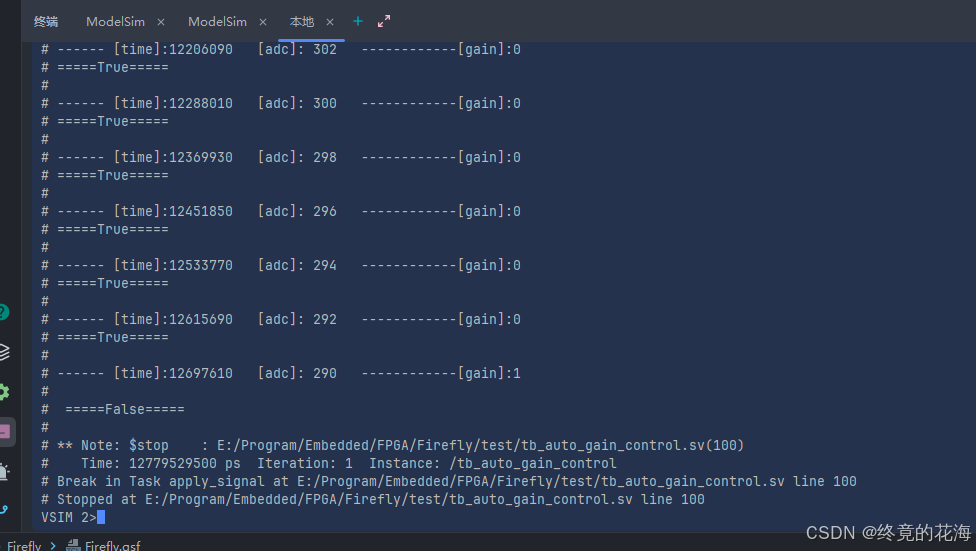

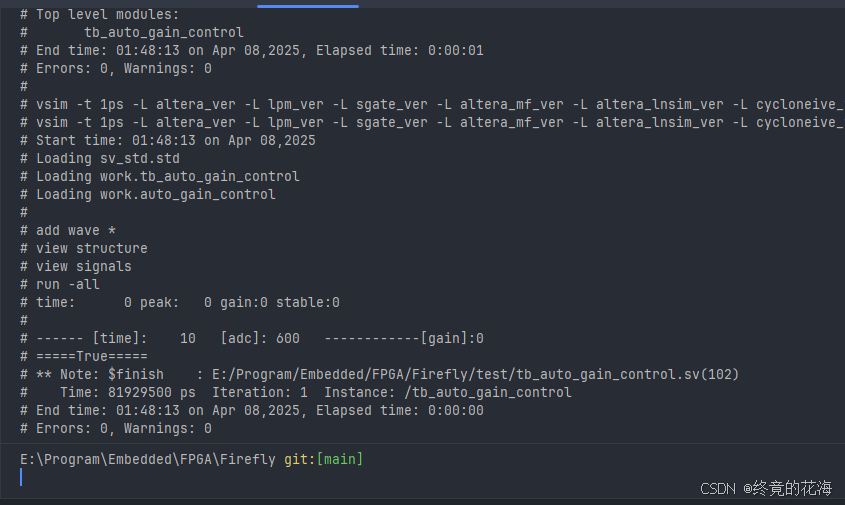

ModelSim(命令行)

前面的ModelSim的GUI有些简陋,那么接下来我们就可以使用命令行模式下的ModelSim,运行结束后让其再执行Surfer。

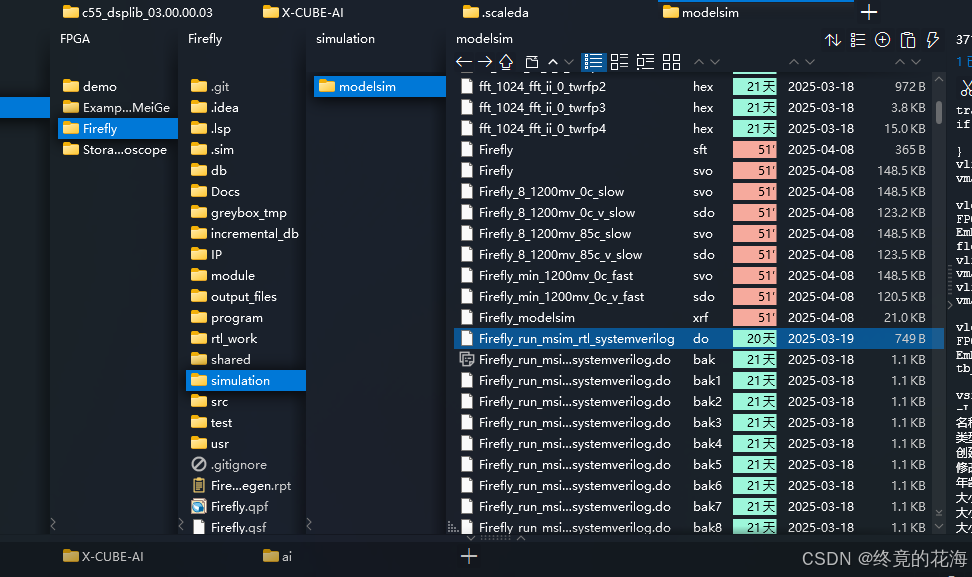

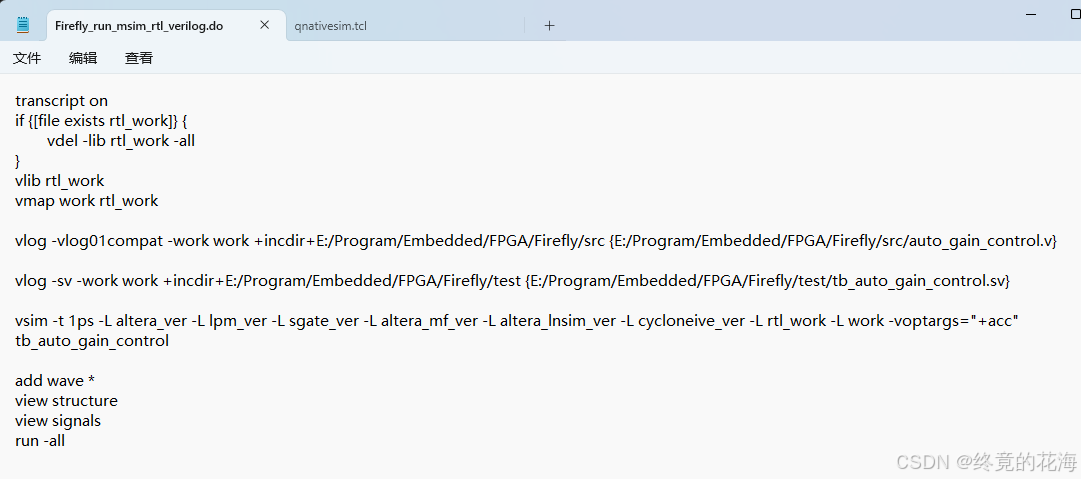

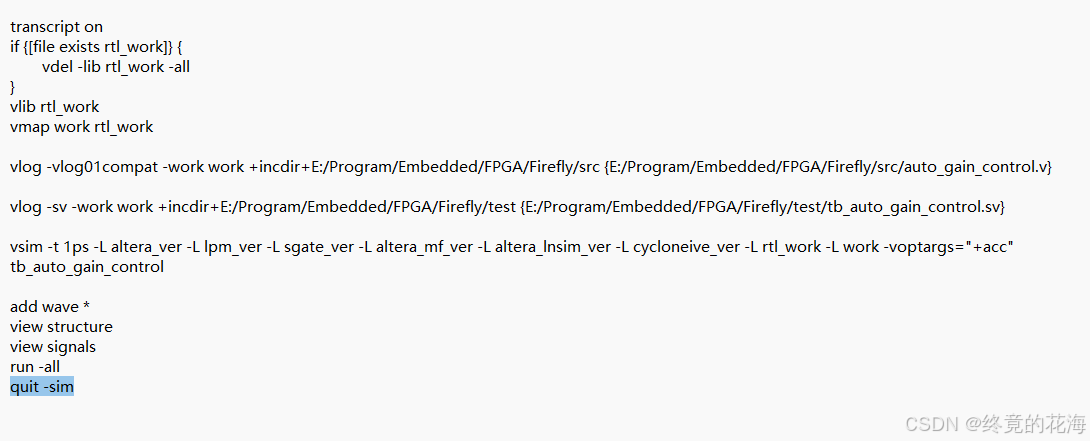

首先我们可以在simulation/modelsim这个目录里找到Quartus自动生成的do脚本,该脚本用于vsim(也就是ModelSim的boss?可以这么说的话)。前面不是提到过Quartus运行RTL仿真时,其实是让quartus_sh执行了tcl脚本,该脚本自动生成了do脚本,并让vsim运行该脚本

脚本的内容很简单,都是些配置和启动命令

因此我们可以让vsim来执行该脚本,并且以命令行的模式(需要带上参数-c),vsim的可执行路径需要自行去找(没有安装ModelSim是没有的,可以搜索“Quartus ModelSim”,会有一堆安装教程)

E:\Tools\Develop\Embedded\intelFPGA\ModelSim\modelsim_ase\win32aloem\vsim -c -do "do E:\\Program\\Embedded\\FPGA\\Firefly\\simulation\\modelsim\\Firefly_run_msim_rtl_verilog.do"可以看到,脚本很顺利地执行下去了,执行后,可能会停留在vism界面(按Ctrl+C可退出)

我们可以在自动生成的do脚本里加上下面这句,即可让其仿真结束后自动退出

那么也就意味着,我们把前面vsim执行do脚本的命令写入到ps1脚本或者bat脚本,再在后面补充上Surfer的命令。那么就可以让其仿真后,自动打开Surfer显示波形了,与之前双击Scaleda的仿真任务无异了

为了进一步简化流程,可以写一个脚本先读取qsf中的顶层文件,再到test目录里去找有没有对应的测试激励文件,然后再生成对应的do脚本,接着让vsim执行仿真,在控制台输出信息,输出完之后,再自动打开Surfer,最后就可以优雅地欣赏波形了

【未完待续】

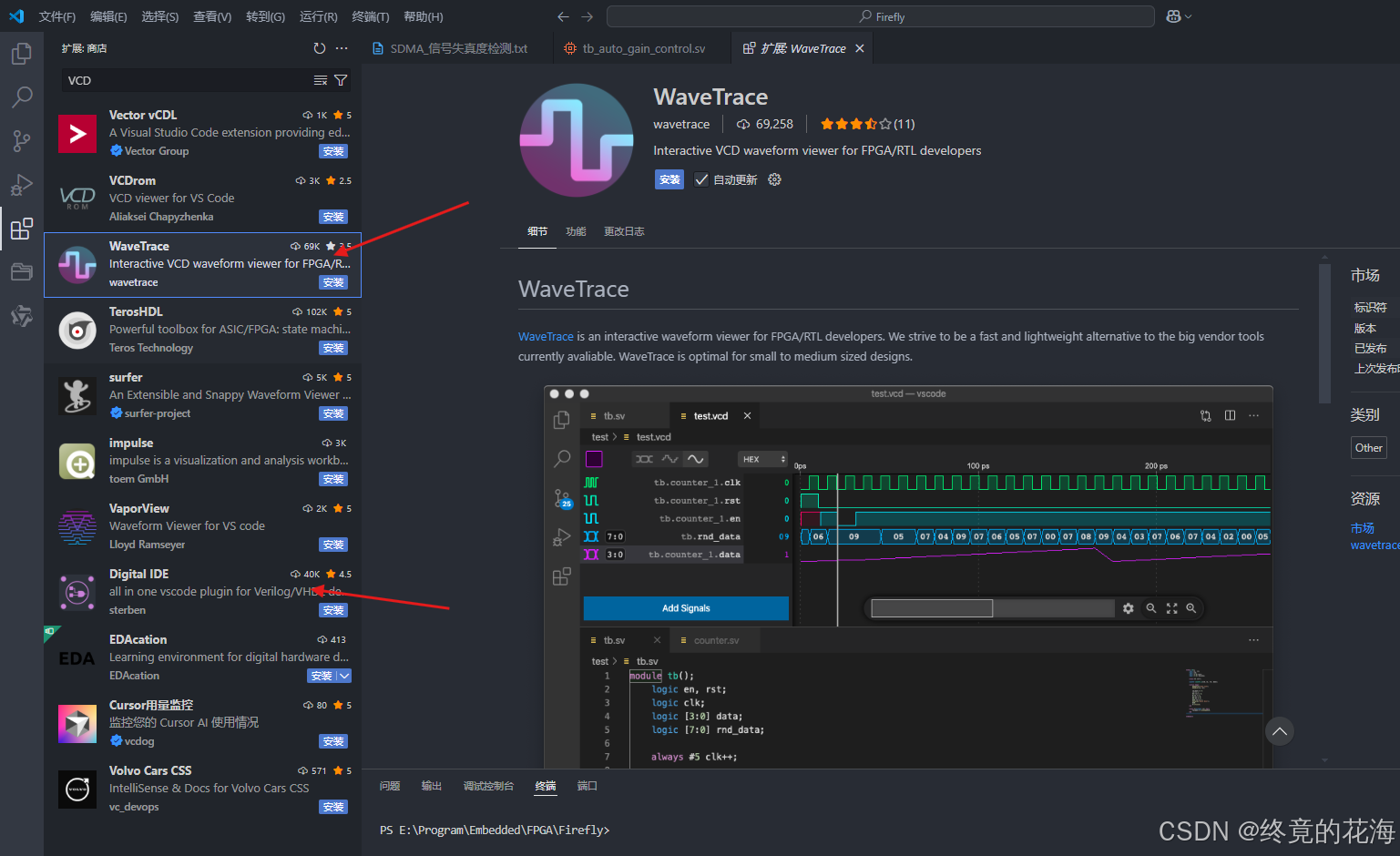

5、波形显示

由于心心念念的Rvcd不能使用,只得另辟蹊径来查看“波形”而非“波形数据”(也就是模拟波形)。在VS Code里可以找到这样的两个插件,完美代替了Rvcd和Surfe

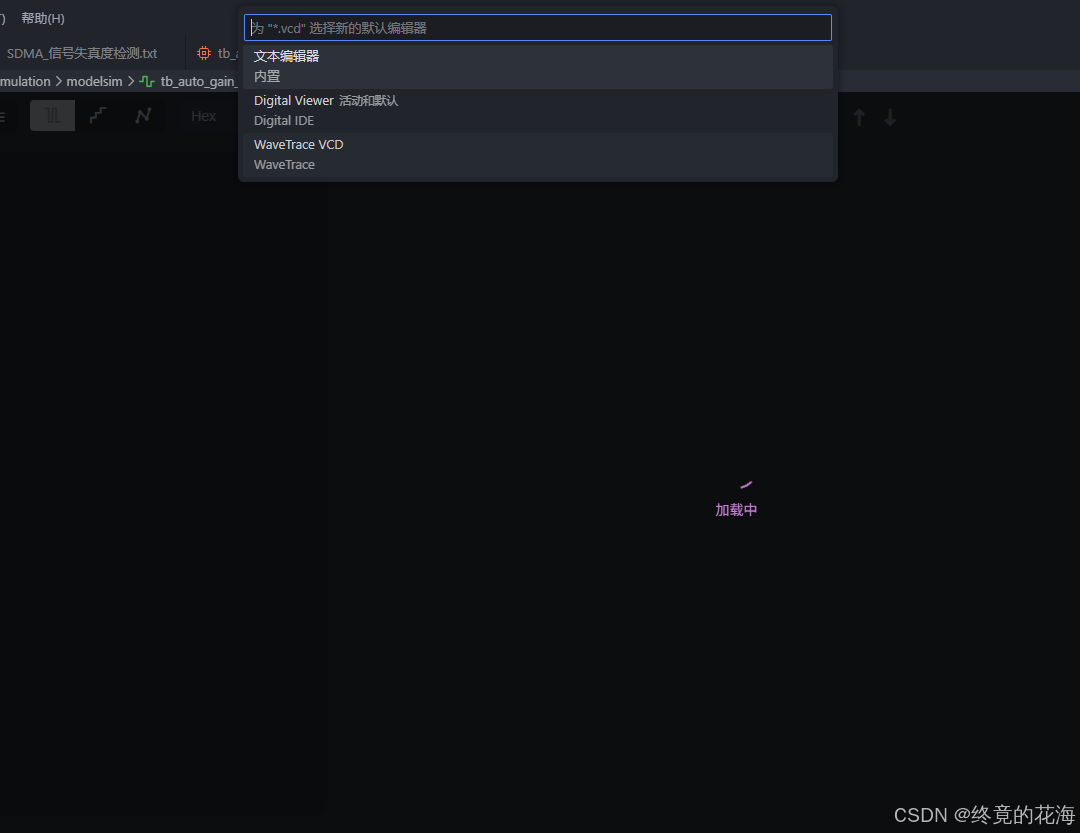

安装插件后,点击生成的vcd文件即可。如果两个插件都安装的话,可以在上方自行切换,二者择其一即可

WaveTrace

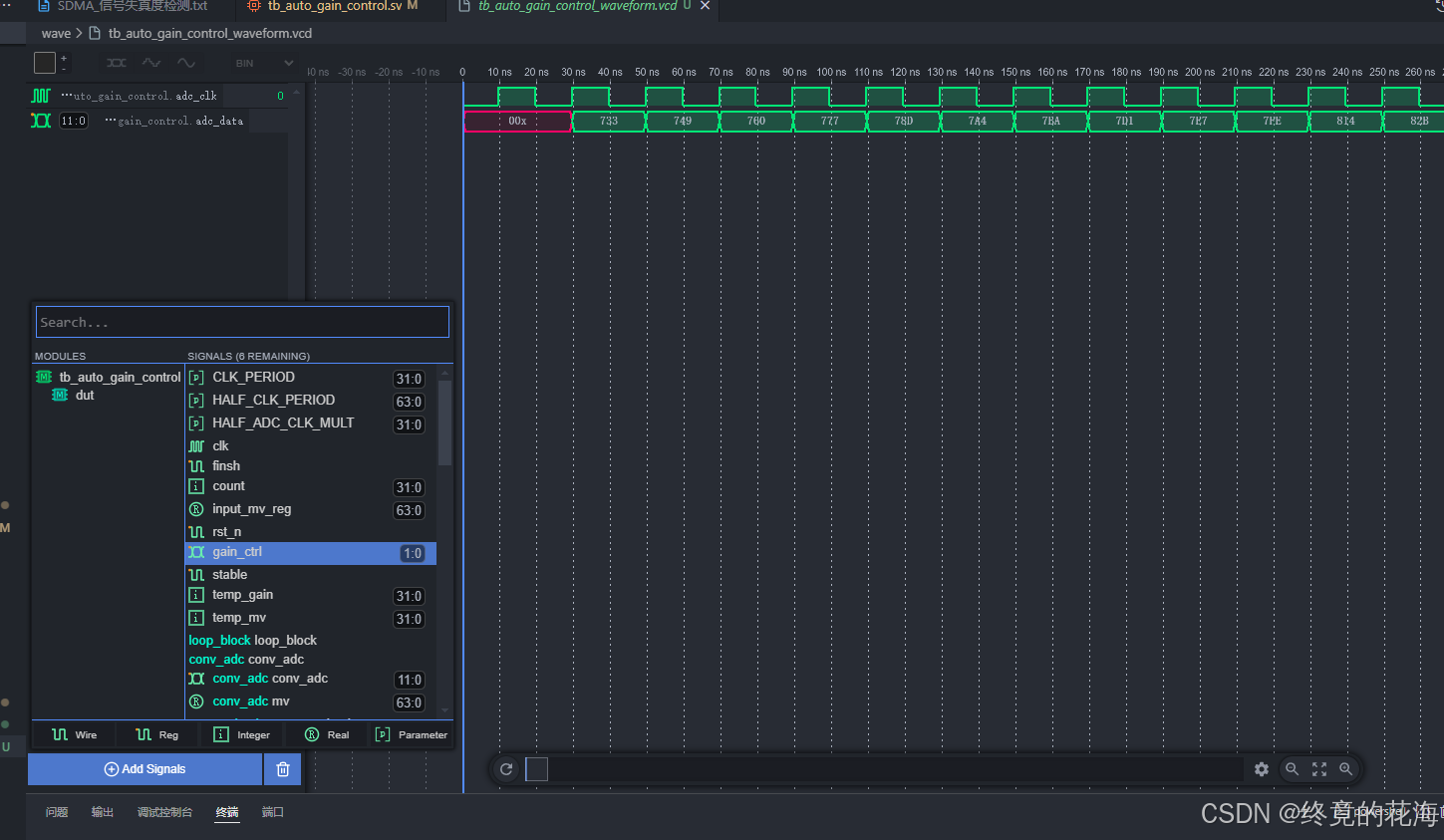

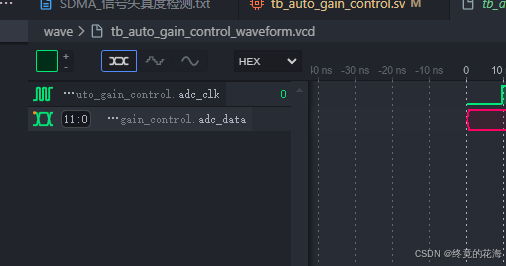

点击左下角的添加信息,双击你要显示的信号即可

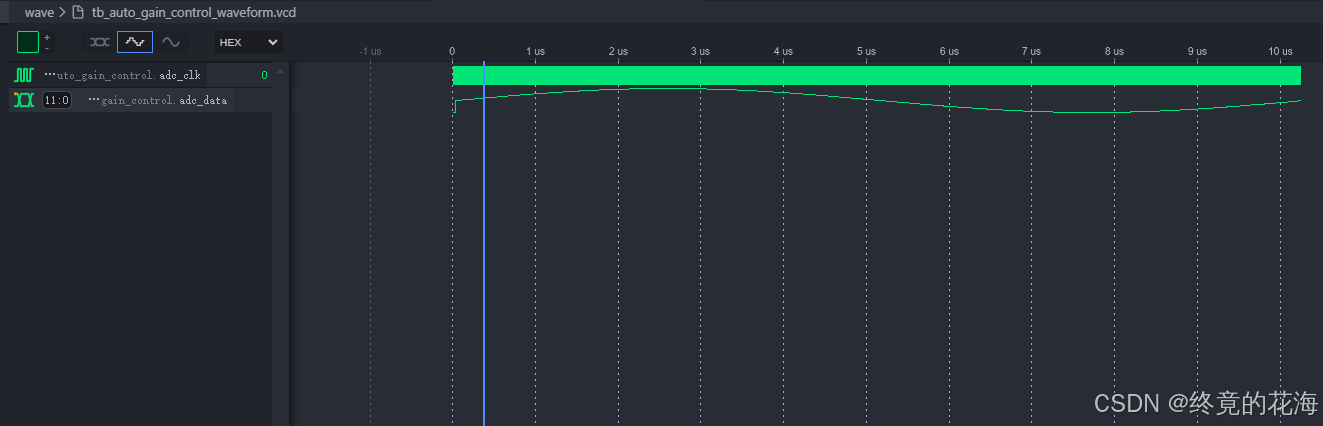

点击左边的信号后,上面会有三个显示类型,分别是数字、数字量化和模拟

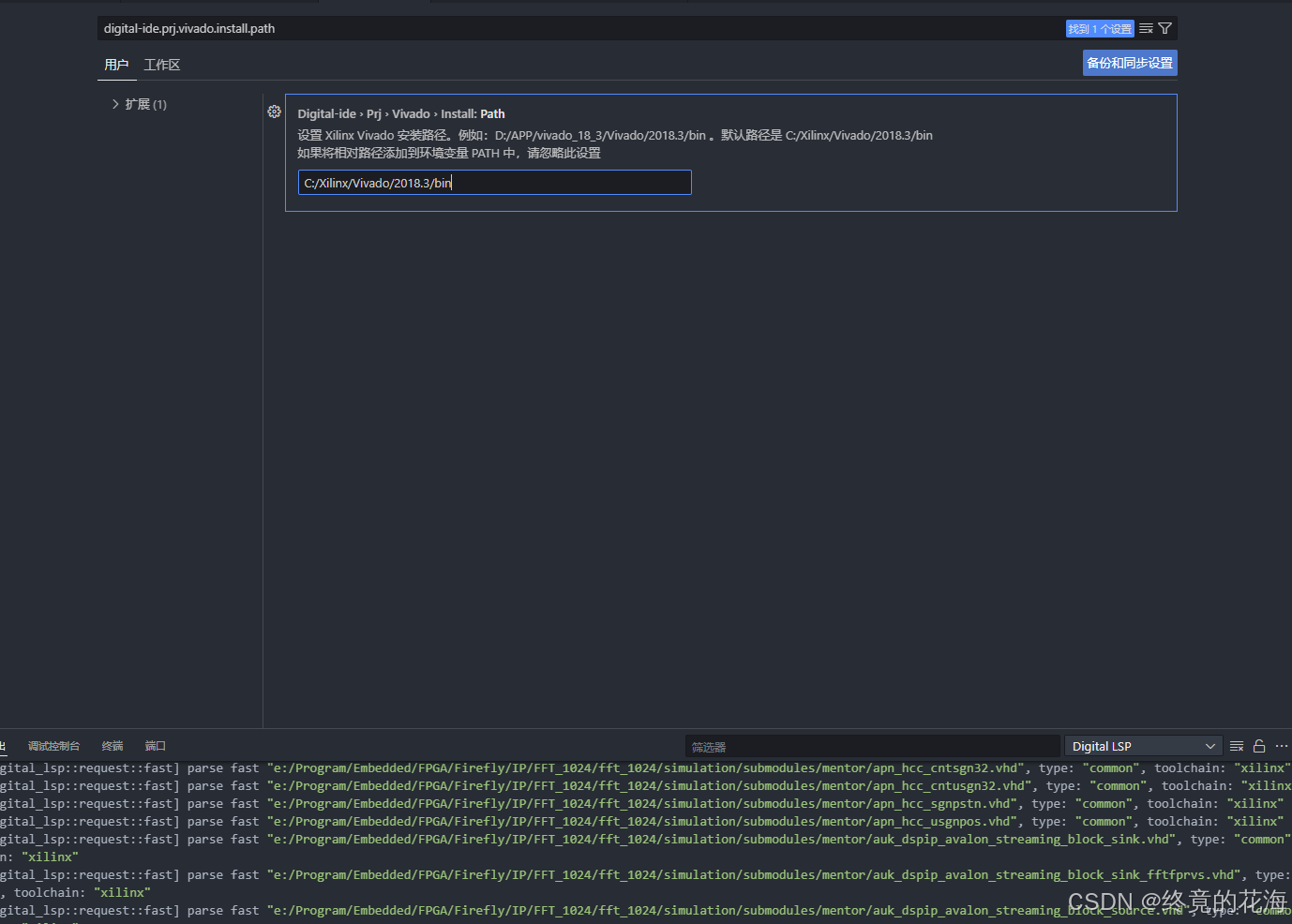

Digital IDE

此插件功能更丰富,但若想使用还需安装Vivado

如此看来,除了内置git外,IDEA在Verilog方面能做到的VS Code都能做到,且某些方面更强

6、分工考虑

编写一些基本模块的话,使用Verilog就足够了,Scaleda中的Verible可以提供非常好的语言支持。此外,git方面,IntelliJ IDEA能提供更好的体验。

仿真的话,仅使用Verilog既冗余、晦涩难懂,又不能很好地达到效果,比如Verilog里没有real、$sin和break等,想要模拟ADC数据采集有些麻烦。而使用System Verilog的话,Scaleda的支持非常差,近乎不能使用,包括里面的仿真任务。此时只能依赖VS Code的hdl_checker插件了,对System Verilog有基本的支持(代码检查)。

如果要对System Verilog进行仿真,那么iverilog就无能为力了,只能使用ModelSim等支持的仿真器。在测试激励文件里可以加上下面这句,以生成波形文件。然后可以在ModelSim仿真后再启动Surfer观察波形(可选项)。

initial begin$dumpfile("xxx.vcd");$dumpvars; end综合起来,编写模块和仿真测试使用IntelliJ IDEA,仿真代码编写方面使用VS Code,资源消耗方面使用Quartus。Scaleda的任务目标由于目前其缺陷性,不太适合使用。

verilator questasim

四、展望

目前来说,想要一站式开发,得需要使用VS Code。IntelliJ IDEA与VS Code关于Verilog的插件并不互通,比如Digtal IDE只在VS Code有,Scaleda只在IntelliJ IDEA上有。两者都是非常优秀的工具,可根据自身开发体验自行选择。

IntelliJ IDEA界面可能更为简介优美,且运行目标由于有现成的框架,想要运行脚本更方便。VS Code更为轻量且插件功能更为丰富,适合一站式开发,但想要达到更好的配置还需着重学习json等,学习难度较大。

VS Code下开发FPGA——FPGA开发体验提升__下-CSDN博客