初始ARM

ARM最基础的组成单元。

最小系统:能系统能够正常工作的最少器件构成的系统 。

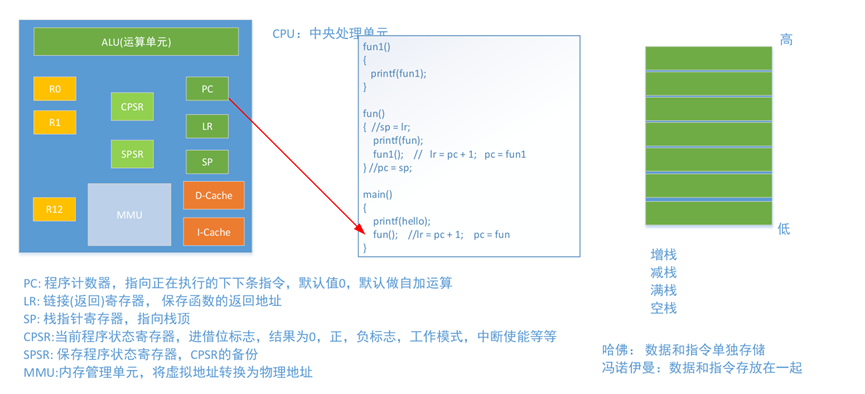

一、CPU基础定义

1. 核心定位

- 计算机三大核心部件:

- CPU(运算与控制)

- 内部存储器(数据存储)

- 输入/输出设备(数据交互)

2. 核心功能

| 功能类型 | 说明 | 典型操作示例 |

|---|---|---|

| 指令解释 | 解析机器码指令 | MOV R0, #0x12 |

| 算术运算 | 执行加减乘除运算 | ADD R1, R2, R3 |

| 逻辑控制 | 实现分支跳转与循环 | BNE loop_label |

| 数据存取 | 管理寄存器与内存交互 | LDR R4, [R5] |

二、指令集架构详解

1. 指令集分类对比

| 特性 | CISC(复杂指令集) | RISC(精简指令集) |

|---|---|---|

| 指令复杂度 | 单指令多操作(如字符串处理) | 单指令单操作 |

| 指令长度 | 变长(1-15字节) | 定长(4字节为主) |

| 执行周期 | 多周期指令占比高 | 单周期指令为主 |

| 典型代表架构 | x86(Intel/AMD) | ARM/RISC-V/PowerPC |

| 应用场景 | 桌面/服务器 | 移动设备/嵌入式系统 |

2. 指令执行流程

graph LRA[取指] --> B[译码]B --> C[执行]C --> D[访存]D --> E[写回]

三、核心寄存器体系

1. 关键专用寄存器

| 寄存器 | 功能说明 | 操作示例 |

|---|---|---|

| PC | 存储下条指令地址 | 0x8000_1004 → 0x8000_1008 |

| LR | 保存函数返回地址 | BL func → LR=0x8000_2000 |

| SP | 堆栈顶地址指针 | PUSH {R0} → SP-=4 |

2. 寄存器位宽演进

| 位宽 | 寻址空间 | 典型处理器 | 技术特点 |

|---|---|---|---|

| 8-bit | 64KB | Intel 8080 | 单任务简单控制 |

| 16-bit | 1MB | Intel 80286 | 段式内存管理 |

| 32-bit | 4GB | ARM Cortex-A8 | 虚拟内存支持 |

| 64-bit | 16EB(艾字节) | Apple M1 | 高级SIMD指令集 |

四、异常处理机制

1. 异常分类

| 类型 | 触发条件 | 处理优先级 |

|---|---|---|

| 复位异常 | 系统上电/硬件复位 | 最高 |

| 硬件中断 | 外设触发(如定时器) | 高 |

| 软件异常 | 非法指令/除零错误 | 中 |

| 系统调用 | SVC指令主动触发 | 可配置 |

五、SoC定义解析

1. 狭义定义

- 核心特征:将计算机系统的关键部件集成到单一芯片中

- 典型集成模块:

- 中央处理器(CPU)

- 图形处理器(GPU)

- 数字信号处理器(DSP)

- 存储器(SRAM/DRAM)

- 外设控制器(USB/PCIe)

- 专用硬件加速模块

2. 广义定义

| 传统系统 | SoC系统 | 核心差异 |

|---|---|---|

| 多芯片分立设计 | 单芯片集成设计 | 集成度提升10-100倍 |

| 板级互连 | 片上总线互连 | 传输延迟降低90% |

| 厘米级尺寸 | 毫米级尺寸 | 体积缩小至1/100 |

六、数据和指令类型

数据类型

ARM 架构采用 32 位架构,支持以下数据类型:

-

Byte(字节)

-

8 位(bits)

-

1 字节(byte)

-

-

Halfword(半字)

-

16 位(bits)

-

2 字节(2 bytes)

-

-

Word(字)

-

32 位(bits)

-

4 字节(4 bytes)

-

-

Doubleword(双字)

-

64 位(bits)

-

8 字节(8 bytes)

-

仅在 Cortex-A 处理器中支持。

-

指令类型

ARM 架构支持两种主要的指令集:

-

ARM 指令集

-

32 位固定长度的指令。

-

适用于高性能计算场景。

-

-

Thumb 指令集

-

16 位固定长度的指令。

-

适用于低功耗和存储受限的场景。

-

Cortex-A 处理器

Cortex-A 处理器支持以下指令集:

-

Thumb-2 指令集

-

混合指令集,支持 16 位和 32 位指令。

-

兼具 Thumb 指令集的存储效率和 ARM 指令集的性能。

-

-

ThumbEE 指令集

-

为嵌入式应用优化的指令集,支持 16 位和 32 位指令。

-

提供额外的指令扩展,适用于动态语言和虚拟机。

-

Jazelle 核心

Jazelle 核心支持:

-

Java bytecode

-

用于直接执行 Java 字节码,提高 Java 应用的性能。

-

七、ARM 基本工作模式

-

User 模式

-

描述:非特权模式,大部分应用程序在此模式下运行。

-

特点:权限受限,无法直接访问硬件或执行特权指令。

-

-

FIQ 模式(Fast Interrupt Request)

-

描述:用于处理高优先级中断。

-

触发条件:当高优先级中断(FIQ)发生时进入。

-

特点:快速响应中断,适合实时性要求较高的场景。

-

-

IRQ 模式(Interrupt Request)

-

描述:用于处理普通优先级中断。

-

触发条件:当普通中断(IRQ)发生时进入。

-

特点:适合处理一般的中断请求。

-

-

Supervisor 模式

-

描述:特权模式,用于操作系统或管理程序。

-

触发条件:复位或执行软中断指令(SWI)时进入。

-

特点:提供对硬件的完全访问权限,适合操作系统内核。

-

-

Abort 模式

-

描述:用于处理存储器访问异常。

-

触发条件:当存储器访问异常(如非法地址访问)发生时进入。

-

特点:允许处理器捕获和处理存储器访问错误。

-

-

Undef 模式(Undefined Instruction)

-

描述:用于处理未定义指令。

-

触发条件:当执行未定义指令时进入。

-

特点:允许处理器捕获和处理非法指令。

-

-

System 模式

-

描述:特权模式,与 User 模式共享寄存器集。

-

触发条件:通常由操作系统使用,用于特权级任务。

-

特点:与 User 模式共享寄存器,但具有特权访问权限。

-

Cortex-A 特有模式

-

Monitor 模式

-

描述:特权模式,用于安全监控代码的执行。

-

触发条件:由安全扩展(TrustZone)触发。

-

特点:支持安全和非安全世界的切换,确保系统安全。

-

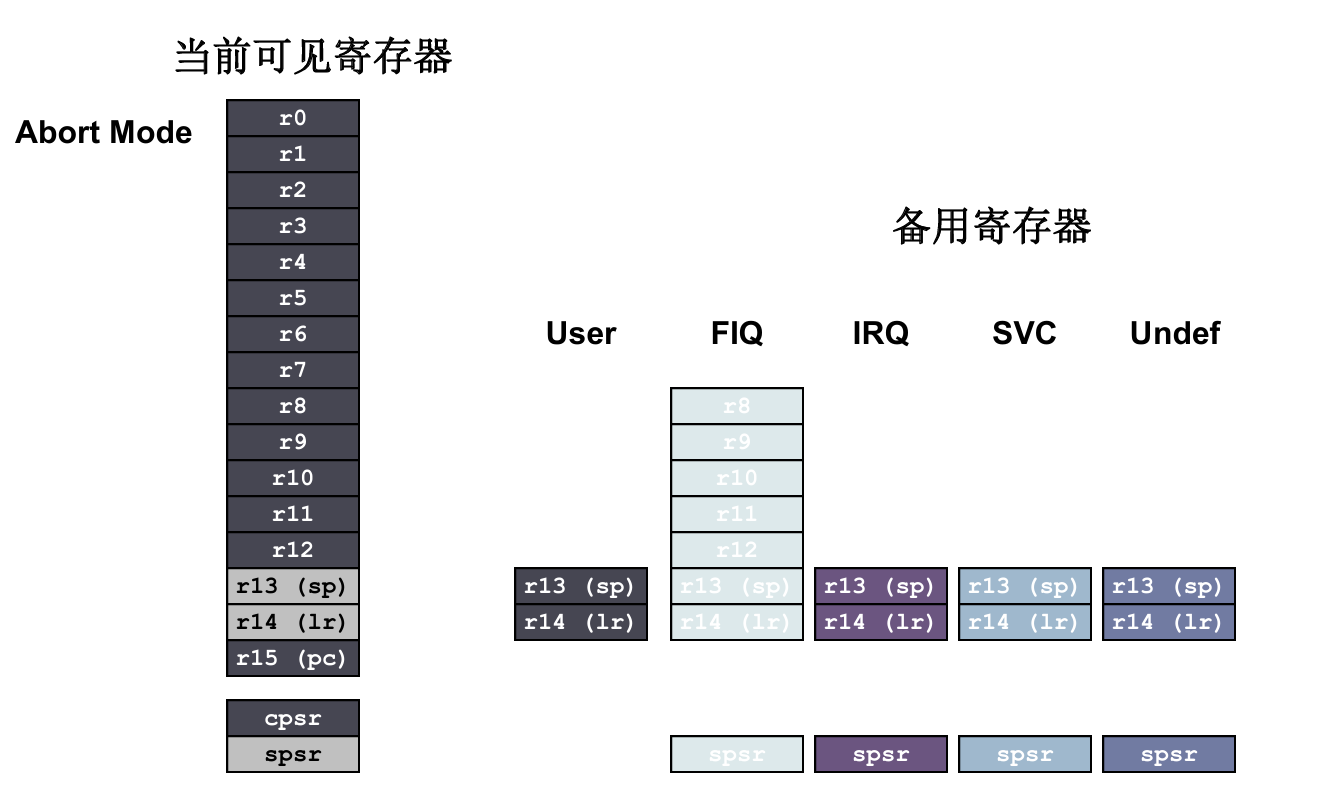

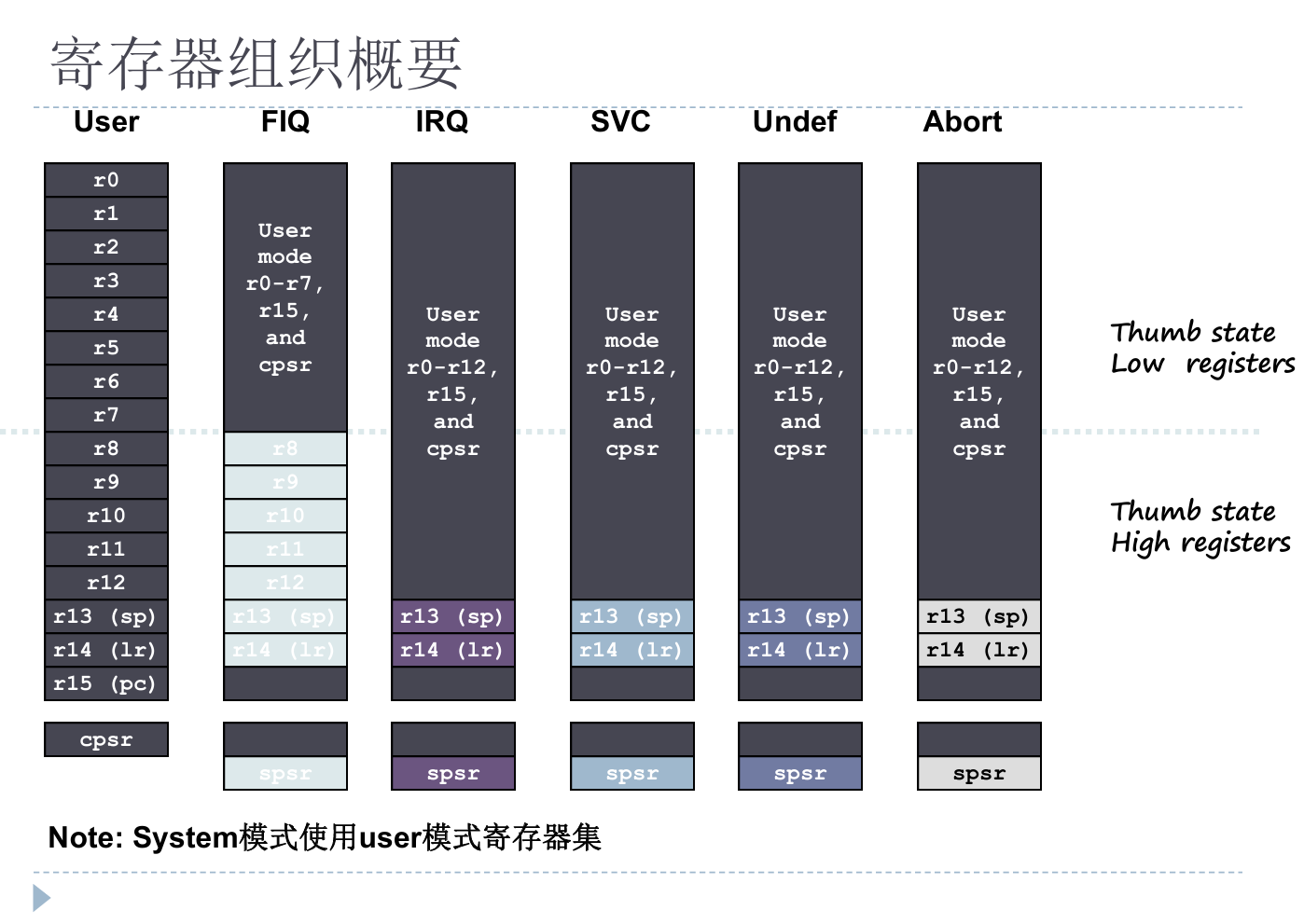

八、ARM 寄存器

RM 处理器共有 37 个寄存器,分为以下几类:

-

通用寄存器(r0-r12)

-

r0-r12:用于数据存储和计算。

-

r13 (sp):堆栈指针(Stack Pointer)。

-

r14 (lr):链接寄存器(Link Register),用于存储子程序返回地址。

-

r15 (pc):程序计数器(Program Counter),指向当前执行指令的地址。

-

-

状态寄存器

-

cpsr:当前程序状态寄存器(Current Program Status Register),包含标志位(如 N、Z、C、V)。

-

spsr:保存的程序状态寄存器(Saved Program Status Register),在异常处理时保存 cpsr 的值。

-

寄存器在不同模式下的分布

ARM 处理器根据不同的工作模式提供不同的寄存器集。以下是各模式下的寄存器分布:

-

User 模式

-

寄存器:r0-r12, r13 (sp), r14 (lr), r15 (pc), cpsr。

-

特点:非特权模式,权限受限。

-

-

FIQ 模式

-

寄存器:r0-r7, r8-r12(专用寄存器),r13 (sp), r14 (lr), r15 (pc), cpsr, spsr。

-

特点:快速中断模式,拥有额外的寄存器(r8-r12)以减少中断处理时的上下文切换。

-

-

IRQ 模式

-

寄存器:r0-r12, r13 (sp), r14 (lr), r15 (pc), cpsr, spsr。

-

特点:普通中断模式,与 User 模式共享大部分寄存器。

-

-

SVC 模式

-

寄存器:r0-r12, r13 (sp), r14 (lr), r15 (pc), cpsr, spsr。

-

特点:超级用户模式,用于操作系统内核。

-

-

Undef 模式

-

寄存器:r0-r12, r13 (sp), r14 (lr), r15 (pc), cpsr, spsr。

-

特点:未定义指令模式,用于处理非法指令。

-

-

Abort 模式

-

寄存器:r0-r12, r13 (sp), r14 (lr), r15 (pc), cpsr, spsr。

-

特点:存储器访问异常模式。

-

Thumb 状态

-

Thumb 状态低寄存器:r0-r7。

-

Thumb 状态高寄存器:r8-r15。

-

特点:在 Thumb 状态下,处理器使用 16 位指令集,寄存器访问受限。

System 模式

-

寄存器:与 User 模式共享相同的寄存器集。

-

特点:特权模式,用于操作系统任务。

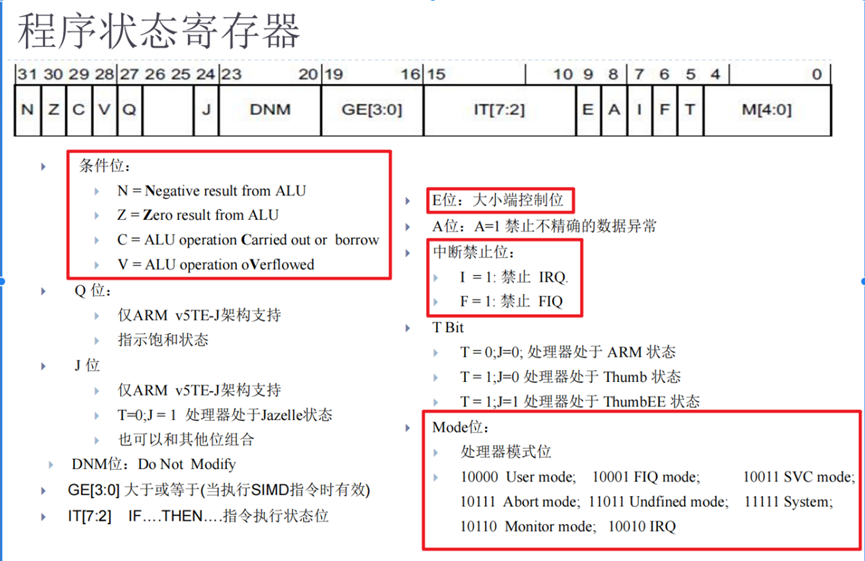

九、程序状态寄存器

九、程序状态寄存器

-

条件位:用于表示 ALU 操作的结果。

-

控制位:用于控制处理器的行为,如大小端模式、中断禁止、指令集状态等。

-

模式位:用于指示处理器的工作模式,包括 User、FIQ、IRQ、SVC、Abort、Undef、System 和 Monitor 模式。

条件位(Condition Flags)

-

N(Negative):ALU 操作结果为负时置位。

-

Z(Zero):ALU 操作结果为零时置位。

-

C(Carry):ALU 操作中发生了进位或借位时置位。

-

V(Overflow):ALU 操作中发生了溢出时置位。

控制位

-

Q 位:仅在 ARM v5TE-J 架构中支持,用于指示饱和状态。

-

J 位:仅在 ARM v5TE-J 架构中支持,用于指示处理器处于 Jazelle 状态。

-

DNM 位(Do Not Modify):保留位,不修改。

-

GE[3:0] 位:大于或等于标志位,当执行 SIMD 指令时有效。

-

IT[7:2] 位:IF...THEN... 指令执行状态位,用于控制条件执行。

大小端控制位(E 位)

-

E 位:控制处理器的大小端模式。

-

E=0:小端模式(Little-endian)。

-

E=1:大端模式(Big-endian)。

-

中断禁止位

-

A 位:禁止不精确的数据异常。

-

A=1:禁止不精确的数据异常。

-

-

I 位:禁止 IRQ 中断。

-

I=1:禁止 IRQ 中断。

-

-

F 位:禁止 FIQ 中断。

-

F=1:禁止 FIQ 中断。

-

T 位(Thumb 状态位)

-

T 位:指示处理器的指令集状态。

-

T=0, J=0:处理器处于 ARM 状态。

-

T=1, J=0:处理器处于 Thumb 状态。

-

T=0, J=1:处理器处于 Jazelle 状态。

-

T=1, J=1:处理器处于 ThumbEE 状态。

-

模式位(M[4:0])

-

模式位:指示处理器的工作模式。

-

10000:User 模式。

-

10001:FIQ 模式。

-

10010:IRQ 模式。

-

10011:SVC 模式。

-

10111:Abort 模式。

-

11011:Undef 模式。

-

11111:System 模式。

-

10110:Monitor 模式。

-

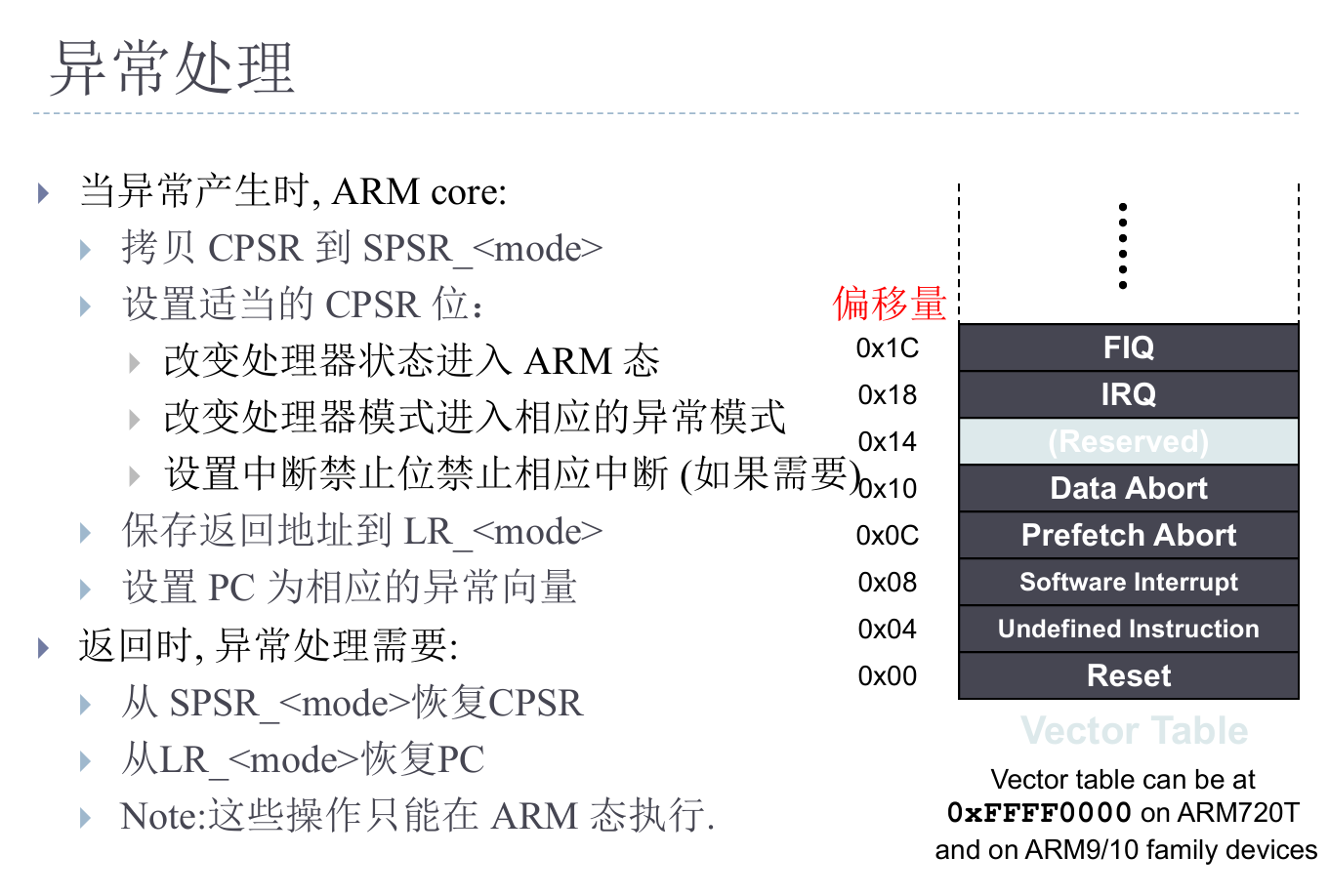

十、异常处理

-

异常处理流程:保存当前状态、设置异常模式、保存返回地址、设置异常向量。

-

异常向量表:用于快速定位异常处理程序的入口地址。

-

异常返回:恢复状态和程序计数器以恢复正常执行。

十一、总结上文

1. ARM 可以工作的模式名字

ARM 处理器有以下工作模式:

-

User 模式:非特权模式。

-

FIQ 模式:快速中断请求模式。

-

IRQ 模式:普通中断请求模式。

-

Supervisor 模式:超级用户模式(特权模式)。

-

Abort 模式:存储器访问异常模式。

-

Undef 模式:未定义指令模式。

-

System 模式:特权模式,与 User 模式共享寄存器集。

-

Monitor 模式(Cortex-A 特有):安全监控模式。

2. ARM 核有多少个寄存器?

ARM 处理器共有 37 个寄存器,包括通用寄存器、状态寄存器和专用寄存器。

3. 什么寄存器用于存储 PC 和 LR 寄存器?

-

PC(程序计数器):由寄存器 r15 存储。

-

LR(链接寄存器):由寄存器 r14 存储。

4. R13 通常用来存储什么?

R13 通常用作 堆栈指针(sp),用于管理堆栈操作。

5. 哪种模式使用的寄存器最少?

User 模式 和 System 模式 使用的寄存器最少,因为它们共享相同的寄存器集。

6. 在 Thumb 指令集中,哪些寄存器处于 Low group?

在 Thumb 指令集中,r0-r7 属于 Low group 寄存器。

7. CPSR 的哪一位反映了处理器的状态?

CPSR 的 T 位 反映处理器的指令集状态:

-

T=0:处理器处于 ARM 状态。

-

T=1:处理器处于 Thumb 状态。

8. 所有的 Thumb 指令采取什么对齐方式?

所有 Thumb 指令采用 2 字节对齐。

9. ARM 有哪几个异常类型?

ARM 支持以下异常类型:

-

Reset:复位。

-

Undefined Instruction:未定义指令。

-

Software Interrupt:软中断(SWI)。

-

Prefetch Abort:预取异常。

-

Data Abort:数据访问异常。

-

IRQ:普通中断请求。

-

FIQ:快速中断请求。

10. 为什么 FIQ 的服务程序地址要位于 0x1C?

FIQ 的服务程序地址位于 0x1C 是因为:

-

异常向量表的偏移量分配中,FIQ 对应的偏移量是 0x1C。

-

这种分配方式确保 FIQ 可以快速响应高优先级中断。

11. 在复位后,ARM 处理器处于何种模式、何种状态?

复位后,ARM 处理器会:

-

进入 Supervisor 模式。

-

处于 ARM 状态。

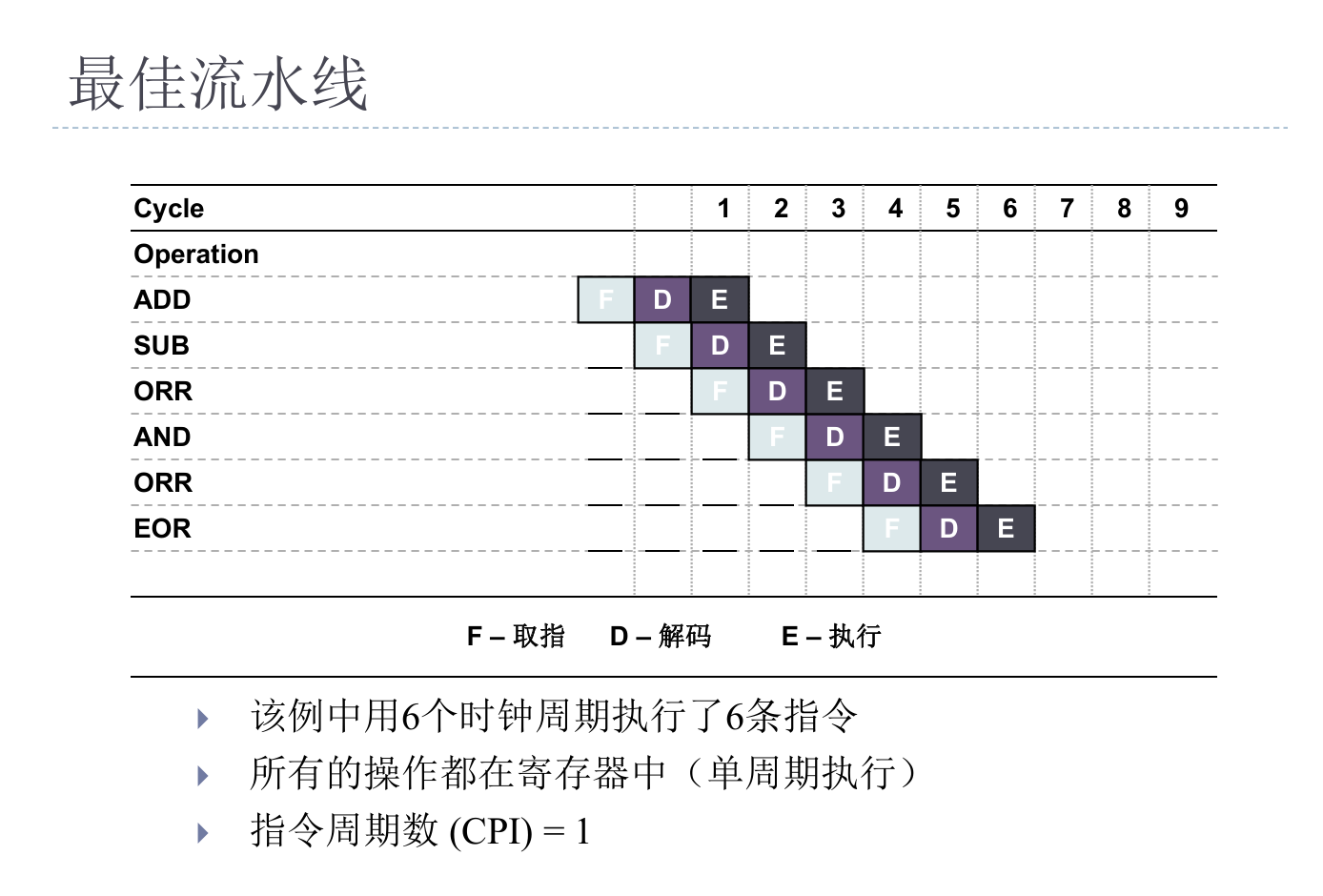

十二、ARM 处理器指令流水线

流水线概述

ARM7 系列处理器使用 3 级流水线 来提高指令流的执行速度。流水线允许多个操作同时处理,而非顺序执行。

流水线阶段

-

Fetch(取指)

-

从存储器中读取指令。

-

在 ARM 状态下,PC 指向当前指令地址。

-

在 Thumb 状态下,PC 指向当前指令地址减去偏移量。

-

-

Decode(解码)

-

解码指令,确定指令中使用的寄存器。

-

在 ARM 状态下,PC 指向当前指令地址减去 4 字节。

-

在 Thumb 状态下,PC 指向当前指令地址减去 2 字节。

-

-

Execute(执行)

-

执行指令,包括寄存器读取、移位操作、ALU 操作和寄存器写回。

-

在 ARM 状态下,PC 指向当前指令地址减去 8 字节。

-

在 Thumb 状态下,PC 指向当前指令地址减去 4 字节。

-

PC 的行为

-

PC 指向正被取指的指令,而非正在执行的指令。

-

在 ARM 状态下,PC 值比正在执行的指令地址大 8 字节。

-

在 Thumb 状态下,PC 值比正在执行的指令地址大 4 字节。

性能指标

-

时钟周期:6 个时钟周期内执行了 6 条指令。

-

CPI(每条指令的时钟周期数):1。

总结

-

流水线优点:通过并行处理多个指令,显著提高了处理器的执行效率。

-

理想状态:在理想情况下,每条指令的 CPI 为 1,即每个时钟周期执行一条指令。