数据通路(Data Path)

王道的课本里面将数据通路的基本结构分为:

- CPU内部单总线方式

- CPU内部多总线方式

- 专用数据通路方式

os:这不是内部总线结构分类嘛,和Data Path有啥关系

而袁书是将这部分内容放在单周期处理器设计里面。

其实也就是这个path太迷惑人了(自我认为)书里还有一句很重要的话,"但不论CPU的内部结构多么复杂,它都可视为由数据通路(Data Path)和控制部件(Control Unit)两大部分组成",那就是就是部件呗,本意可能也是为了方便理解数据流和控制流怎么走的吧。

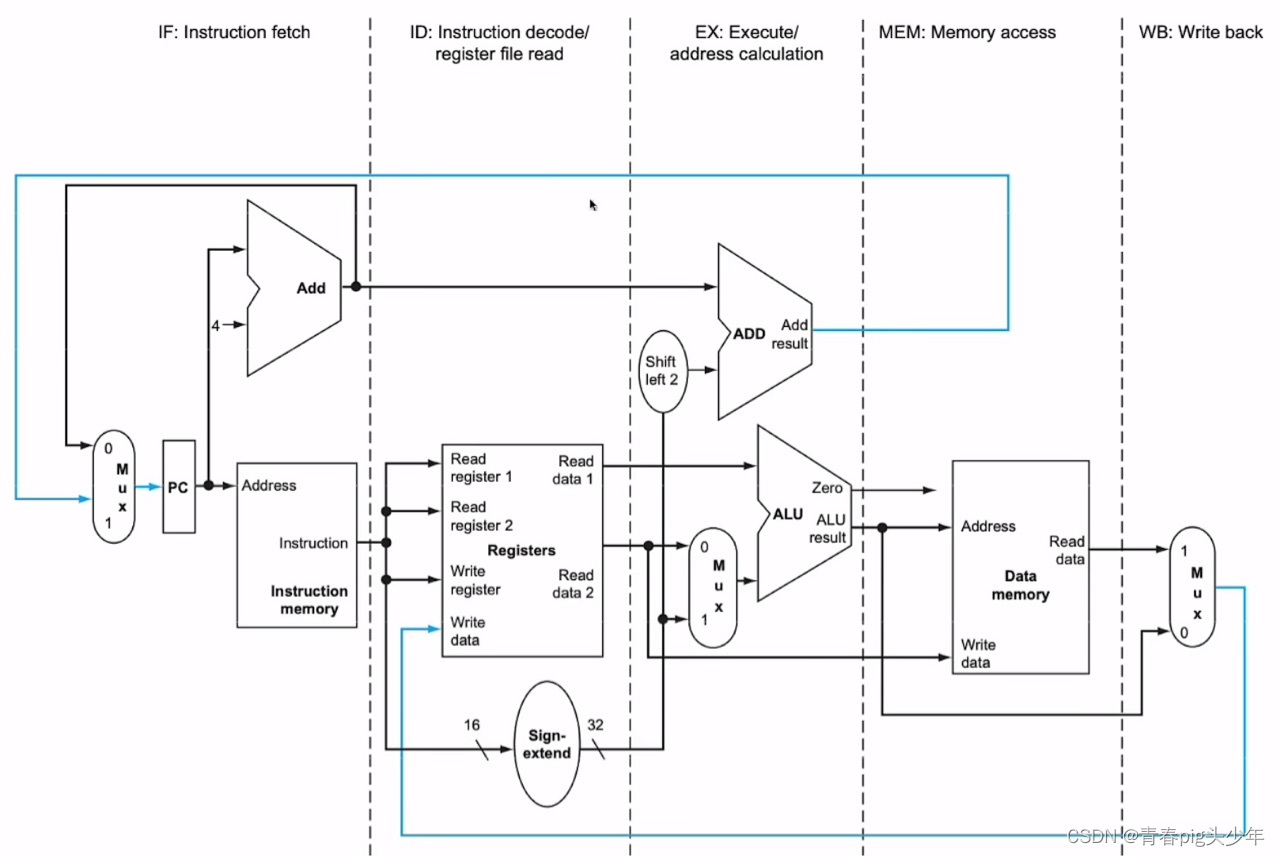

那其实要我说咱408扣它这个干啥?真题里头无非不就是考指令的IF、ID、EX、MEM、WB这些阶段指令是数据是怎么流通的嘛,然后再加上控制信号。那不就还是pipeline那张图嘛,可为啥大题写不出来呢?

(因为被人家把寄存器组具体给你展开了,吓🐭了)

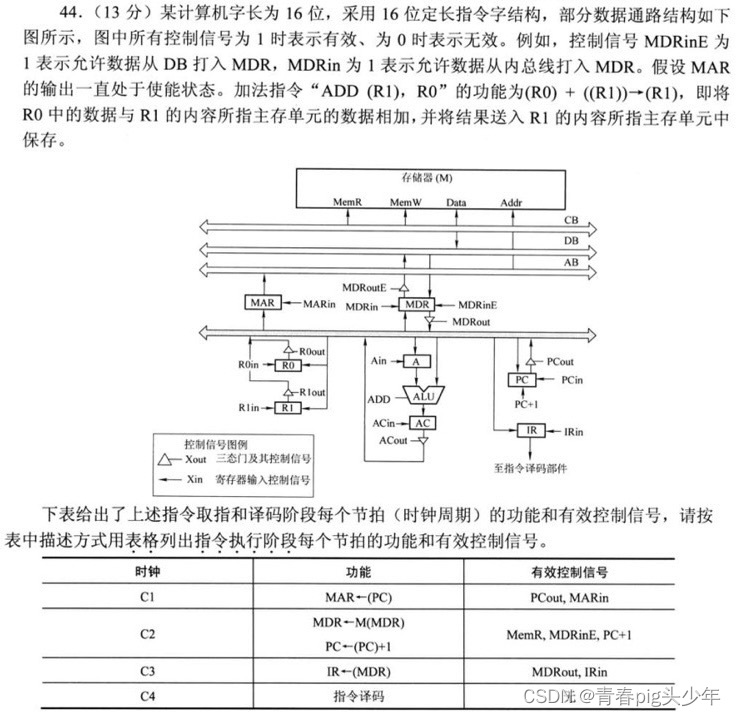

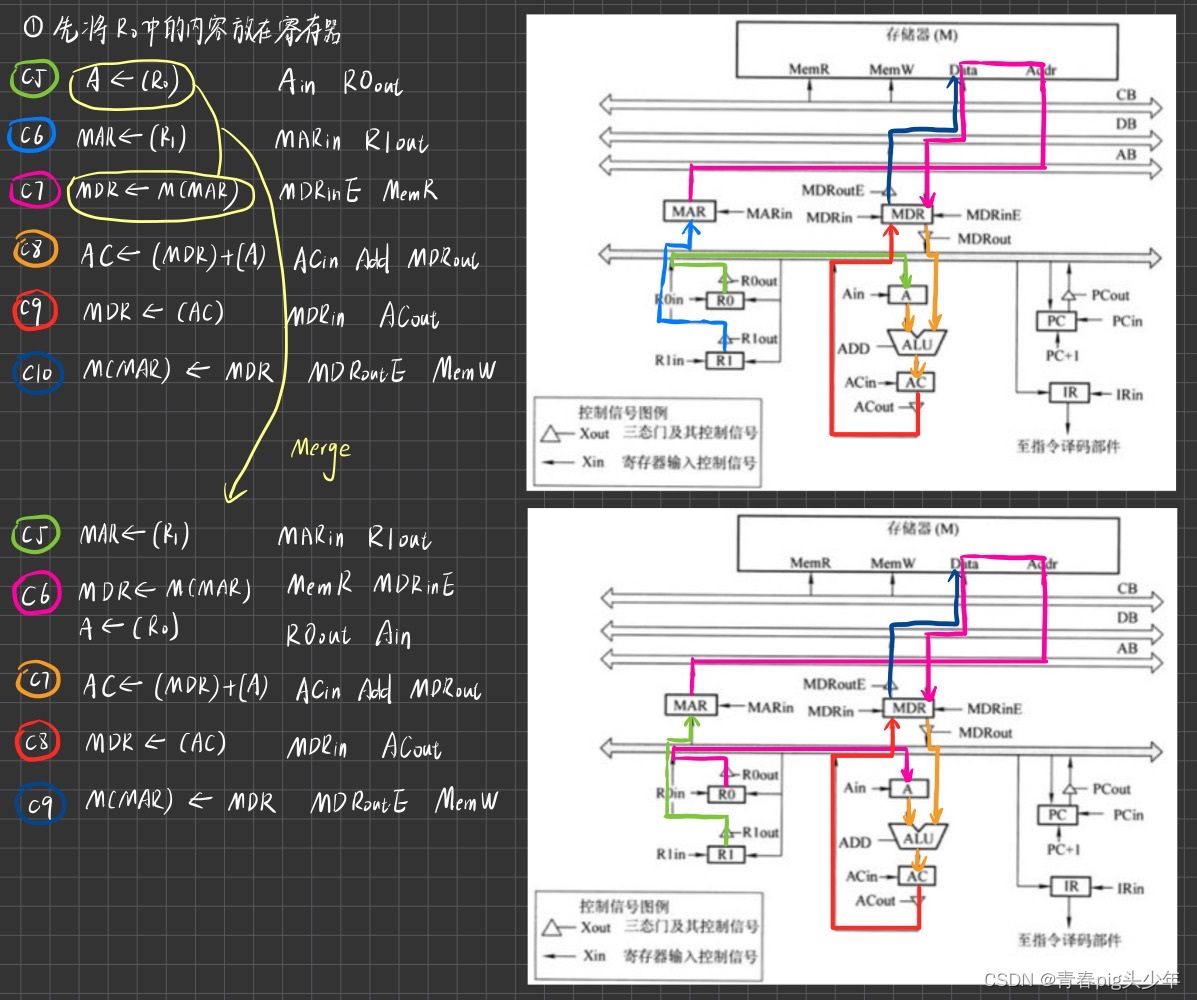

先分析一波题干,发现也没讲啥要注意的就是MDRin和MDRinE的区别,但这个其实看图也能看出来。

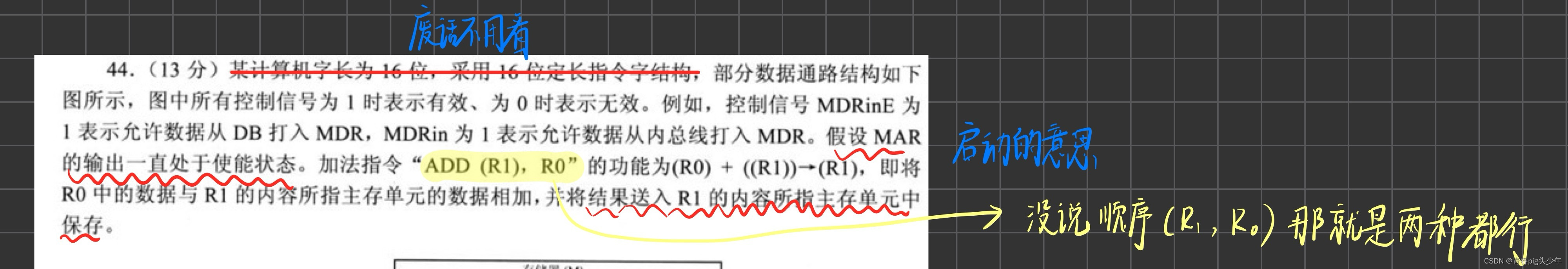

那发现是不是这题答案不唯一啊,因为没有规定R0,R1的顺序所以说无论先1后0还是先0后1都是可以的。

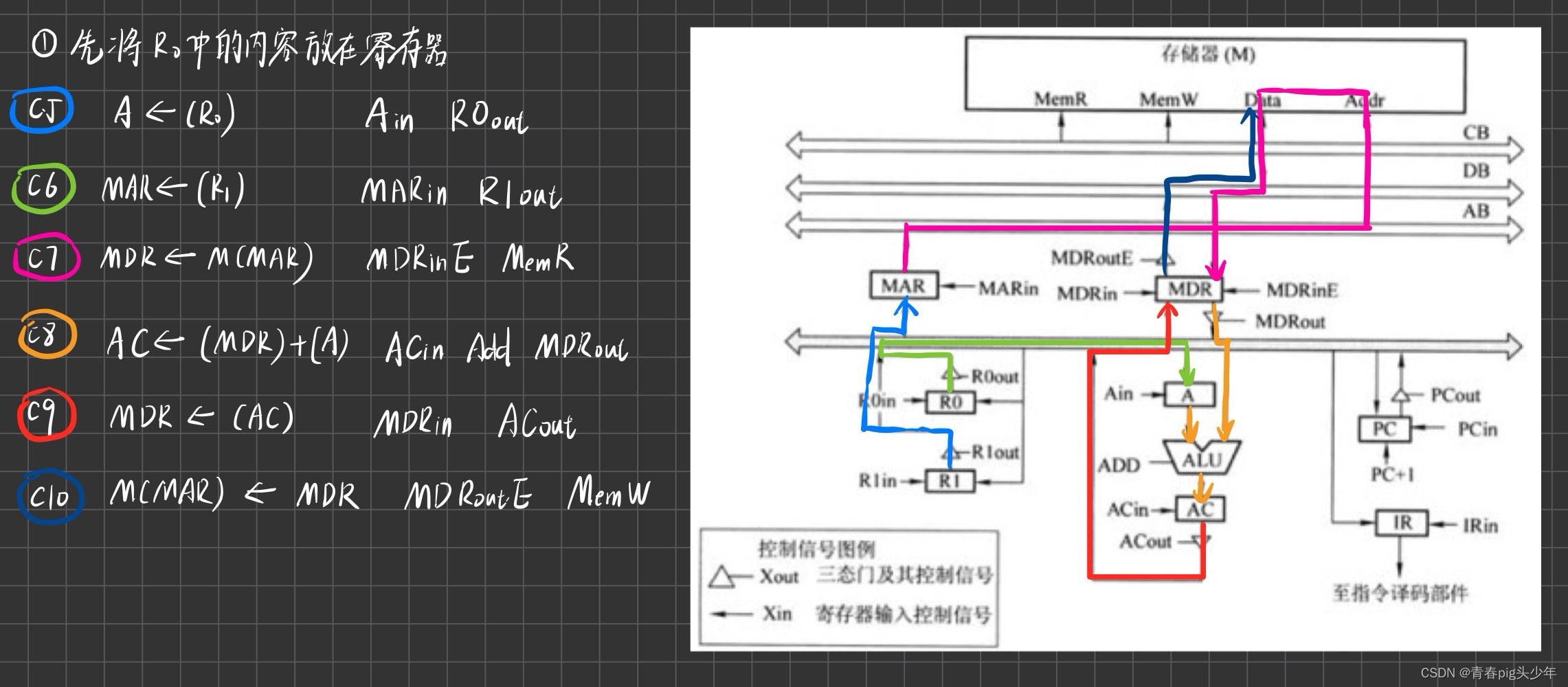

画完这个图了,其实就发现这个是不是还可以再优化一下啊,因为C5和C7即使一块运行也不冲突呀,那这样不就省下了一个时钟周期嘛。(当然题目并没有要求最少时钟周期完成蛤)

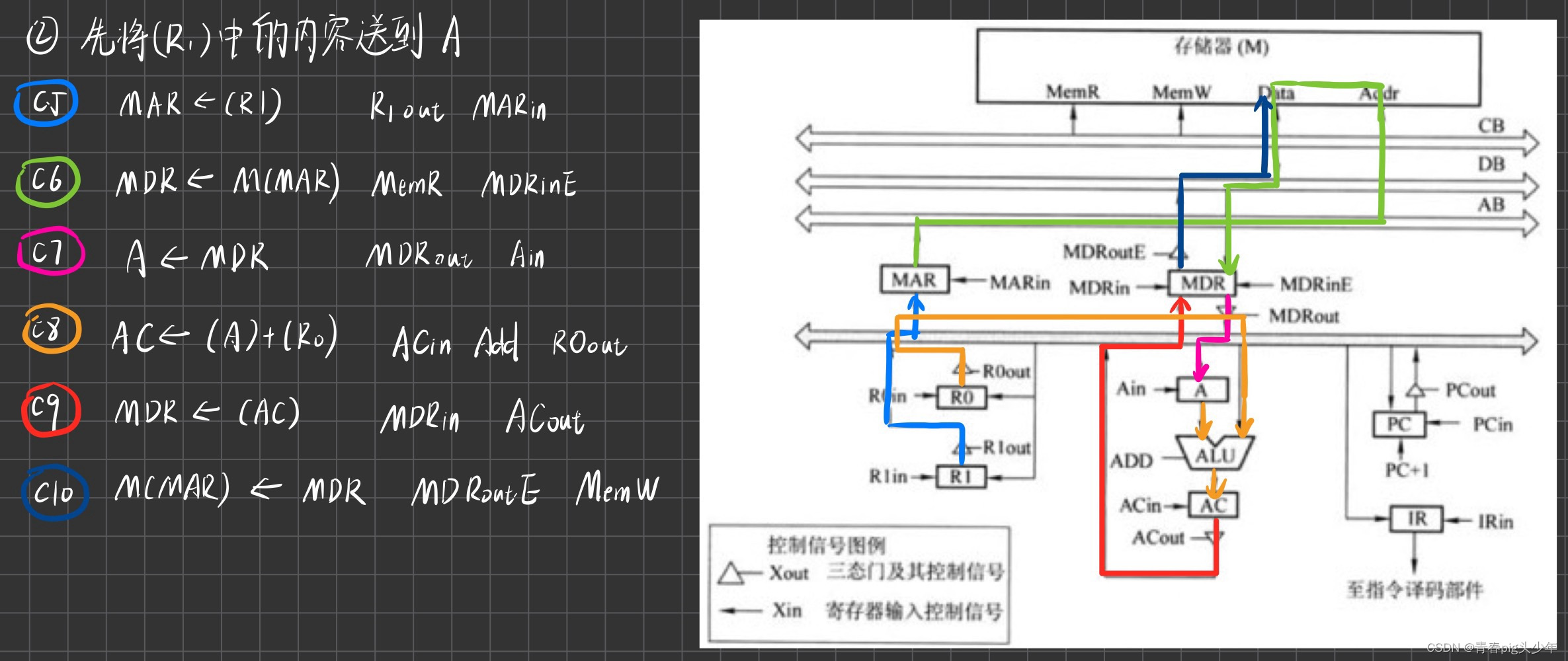

我们再看第二种情况。

是不是发现了,考察的就还是指令的数据流啊。

(后续刷到22年我再更)